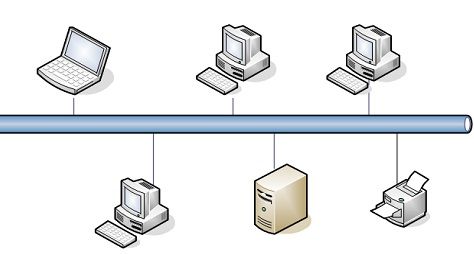

Proces navrhovania digitálneho hardvéru sa za posledných niekoľko rokov intenzívne zmenil. Malé digitálne obvody teda možno implementovať pomocou PAL a PLA. Používa sa každé zariadenie implementovať rôzne obvody ktoré nepotrebujú viac ako počet i / ps, o / ps a produktových podmienok ponúkaných v konkrétnom čipe. Tieto čipy sú nedostatočné na pomerne skromné veľkosti, zvyčajne podporujú vzájomný počet vstupov a výstupov nie viac ako 32. Na návrh týchto obvodov, ktoré potrebujú viac vstupov a výstupov, je možné použiť buď početné PLA / PAL, alebo klasickejší typ. čipu sa dá nazvať CPLD (komplexné programovateľné logické zariadenie). Čip CPLD obsahuje niekoľko blokov obvodov na jednom čipe s vnútornými zdrojmi vodičov na pripojenie obvodových blokov. Každý obvodový blok je porovnateľný s PLA alebo PAL.

Čo je to zložité programovateľné logické zariadenie?

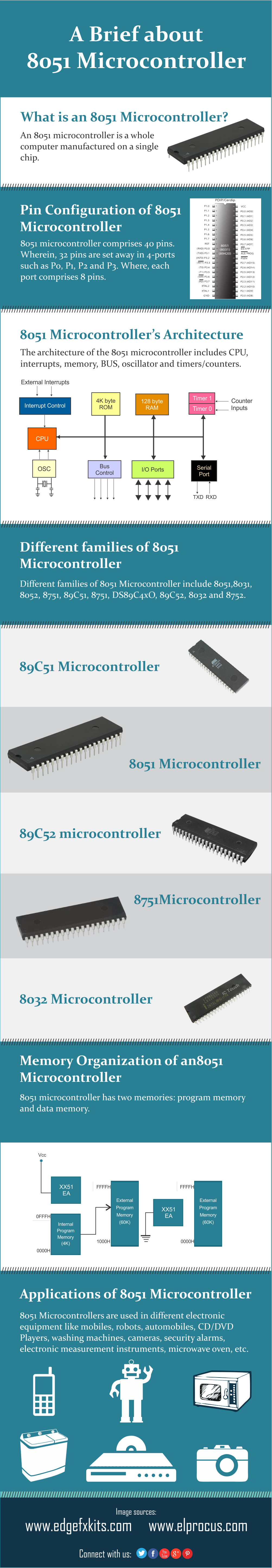

Skratka CPLD je „Komplexné programovateľné logické zariadenia“, je to jedna druh integrovaného obvodu ktoré návrhári aplikácií navrhujú na implementáciu digitálneho hardvéru, ako sú mobilné telefóny. Dokážu zvládnuť vedome vyšší dizajn ako SPLD (jednoduché programovateľné logické zariadenia), ale ponúkajú menej logiky ako FPGA ( poľné programovateľné hradlové polia ). CPLD obsahujú početné logické bloky, každý z týchto blokov obsahuje 8 - 16 makrobuniek. Pretože každý logický blok vykonáva určitú funkciu, všetky makrobunky v logickom bloku sú úplne spojené. V závislosti na použití môžu byť tieto bloky navzájom spojené alebo nie.

Komplexné programovateľné logické zariadenie

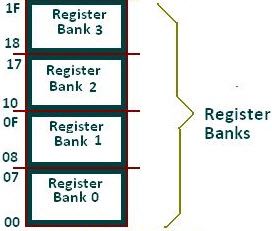

Väčšina CPLD (komplexné programovateľné logické zariadenia) majú makrobunky so súčtom logických funkcií a voliteľnou hodnotou FF (klopný obvod) . V závislosti od čipu podporuje kombinatorická logická funkcia od 4 do 16 produktových termínov s možnosťou fan-in. CPLD sa líšia aj z hľadiska posuvných registrov a logických hradiel. Z tohto dôvodu môžu byť namiesto FPGA použité CPLD s veľkým počtom logických hradiel. Ďalšia špecifikácia CPLD označuje počet výrazov produktu, ktoré môže makrobunka dosiahnuť. Výrazy produktu sú produktom digitálnych signálov, ktoré vykonávajú špecifickú logickú funkciu.

CPLD sú k dispozícii v niekoľkých formách balíkov IC a logických rodinách. CPLD sa tiež líšia, pokiaľ ide o napájacie napätie, prevádzkový prúd, pohotovostný prúd a stratu energie. Okrem toho je možné ich získať s rôznymi veľkosťami pamäte a rôznymi druhmi podpory pamäte. Pamäť sa zvyčajne vyjadruje v bitoch / megabitoch. Podpora pamäte pozostáva z ROM, RAM a dvojportovej RAM. Skladá sa tiež z CAM (obsah adresovateľnej pamäte), ako aj FIFO (first-in, first-out) pamäte a LIFO (last-in, last-out) pamäte.

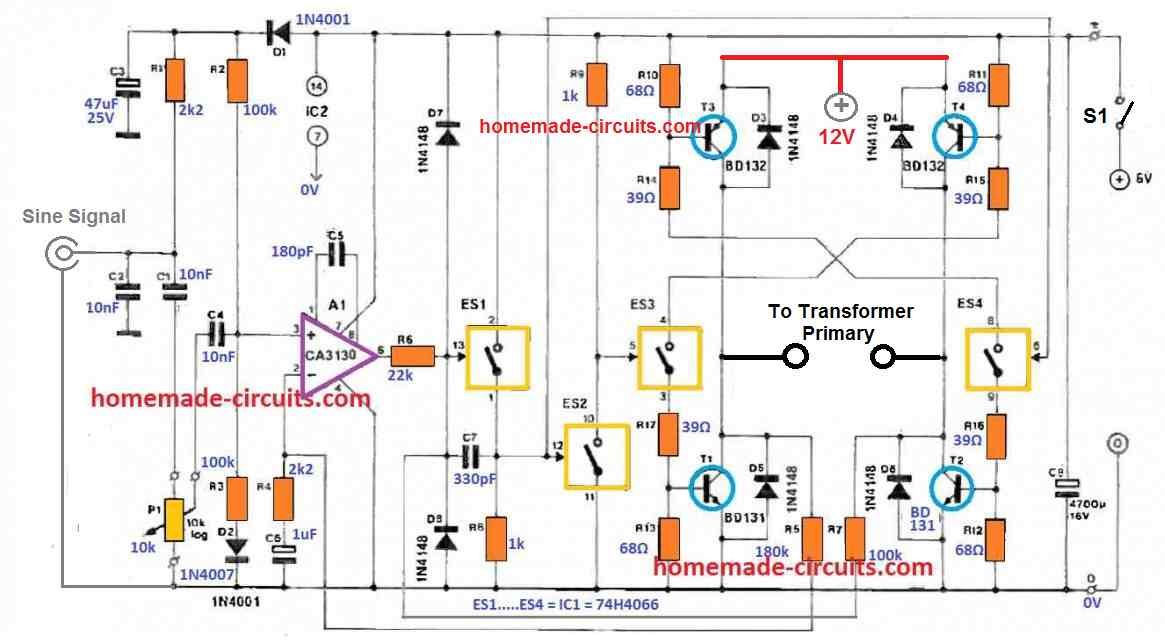

Architektúra komplexného programovateľného logického zariadenia

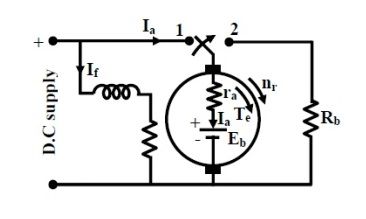

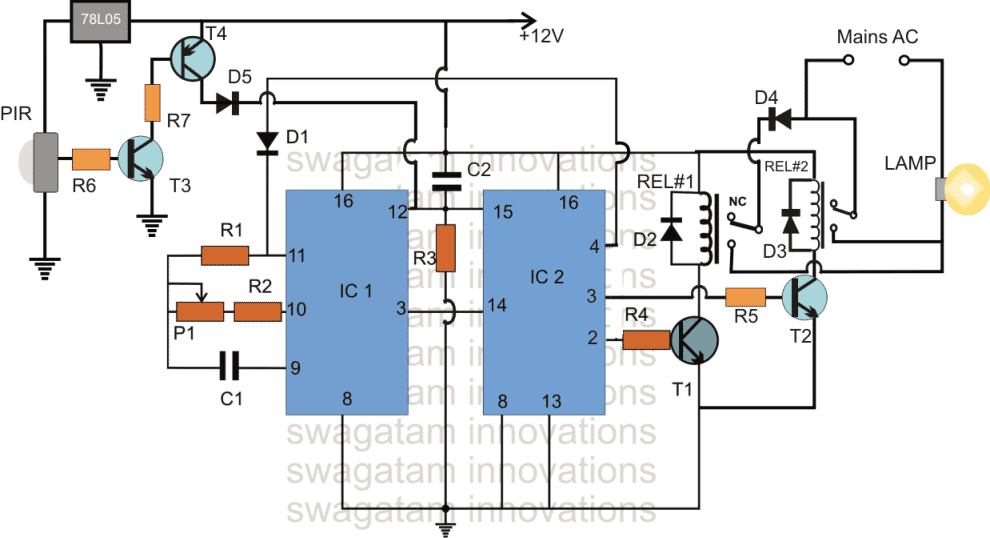

Komplexné programovateľné logické zariadenie pozostáva zo skupiny programovateľných FB (funkčných blokov). Vstupy a výstupy týchto funkčných blokov sú navzájom spojené pomocou GIM (globálna prepojovacia matica). Táto prepojovacia matica je rekonfigurovateľná, takže môžeme upravovať kontakty medzi funkčnými blokmi. Budú existovať niektoré vstupné a výstupné bloky, ktoré nám umožnia zjednotiť CPLD s vonkajším svetom. Architektúra CPLD je uvedená nižšie.

Programovateľný FB všeobecne vyzerá ako pole logických brán , kde je možné programovať pole brán AND a brány OR sú stabilné. Ale každý výrobca má svoj spôsob uvažovania, ako navrhnúť funkčný blok. Uvedený o / p možno nájsť prevádzkovaním spätnoväzbových signálov získaných z výstupov brány OR.

Architektúra CPLD

V programovaní CPLD je návrh najskôr kódovaný v jazyku Verilog alebo VHDL, akonáhle je kód (simulovaný a syntetizovaný.) Počas syntézy je ručne vybraný model CPLD (cieľové zariadenie) a je vytvorený zoznam mapovacích sietí založený na technológii. Tento zoznam je možné uzavrieť -prispôsobenie sa skutočnej architektúre CPLD pomocou procesu umiestnenia a trasy, ktoré sa zvyčajne dosahuje softvérom typu „miesto a smer“, ktorý vlastní proprietárny softvér spoločnosti CPLD. Potom operátor vykoná určité potvrdzovacie procesy. Ak je všetko dobré, použije CPLD, inak prestaví to.

Problémy architektúry CPLD

Pri zvažovaní zložitého programovateľného logického zariadenia na použitie v dizajne je možné vziať do úvahy nasledujúce problémy s architektúrou

- Programovacia technológia

- Schopnosť funkčného bloku

- Schopnosť I / O

Patria sem niektoré rodiny CPLD od rôznych maloobchodníkov

- Rodiny Altera MAX 7000 a MAX 9000

- Rodiny ATMEL a ATV

- Rodina LSI mriežkových ispov

- Rodina MACH z Lattice (Vantis)

- Rodina Xilinx XC9500

Rodiny CPLD

Aplikácie CPLD

Aplikácie CPLD zahŕňajú nasledujúce

- Komplexné programovateľné logické zariadenia sú ideálne pre aplikácie s vysokým výkonom a kritickým riadením.

- CPLD sa môže v digitálnych dizajnoch používať na vykonávanie funkcií zavádzača

- CPLD sa používa na načítanie konfiguračných údajov poľa programovateľného hradlového poľa z energeticky nezávislej pamäte.

- Spravidla sa používajú v malých dizajnových aplikáciách, ako je dekódovanie adries

- CPLD sa často používajú v mnohých aplikáciách, napríklad v nákladných prenosných zariadeniach napájaných z batérie, a to kvôli ich malým rozmerom a nízkej spotrebe energie.

Jedná sa teda o komplexnú architektúru programovateľných logických zariadení a jej aplikácií. Dúfame, že ste tomuto konceptu lepšie porozumeli. Ďalej akékoľvek otázky týkajúce sa tohto konceptu resp realizovať akékoľvek elektrické a elektronické projekty , prosím, poskytnite svoje cenné návrhy komentárom v sekcii komentárov nižšie. Tu je otázka, aký je rozdiel medzi CPLD a FPGA?

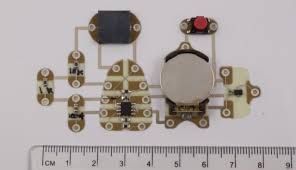

Fotografické úvery:

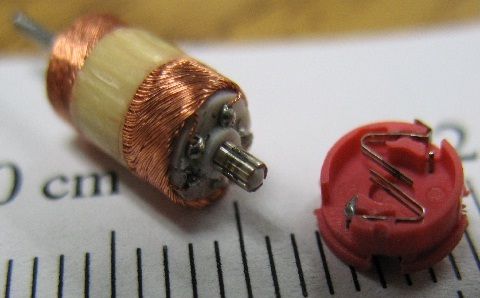

- CPLD wikimedia

- Architektúra CPLD slidesharecdn