The tranzistor s efektom poľa (FET) je elektronické zariadenie, v ktorom elektrické pole sa používa na reguláciu prietoku prúdu. Na realizáciu tohto sa aplikuje potenciálny rozdiel cez hradlové a zdrojové svorky zariadenia, čo mení vodivosť medzi odtokovou a zdrojovou svorkou a spôsobuje, že cez tieto svorky preteká riadený prúd.

FET sa nazývajú unipolárne tranzistory pretože sú navrhnuté tak, aby fungovali ako zariadenia s jedným nosičom. Nájdete rôzne dostupné tranzistory s efektom poľa.

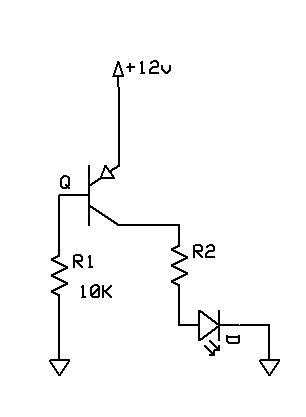

Symbol

Grafické symboly pre JFET pre n-kanál a p-kanál je možné vizualizovať na nasledujúcich obrázkoch.

Môžete si jasne všimnúť, že značky šípok smerujúce dovnútra zariadenia s n-kanálom označujú smer, ktorým som jaG(prúd brány) má prúdiť, keď bol prechod p-n predpätý.

V prípade zariadenia s kanálom p sú podmienky rovnaké, až na rozdiel v smere šípky.

Rozdiel medzi FET a BJT

Tranzistor s poľným efektom (FET) je trojpólové zariadenie určené pre širokú škálu obvodových aplikácií, ktoré na vysokej úrovni dopĺňajú tranzistor BJT.

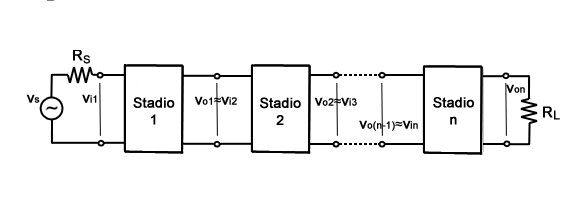

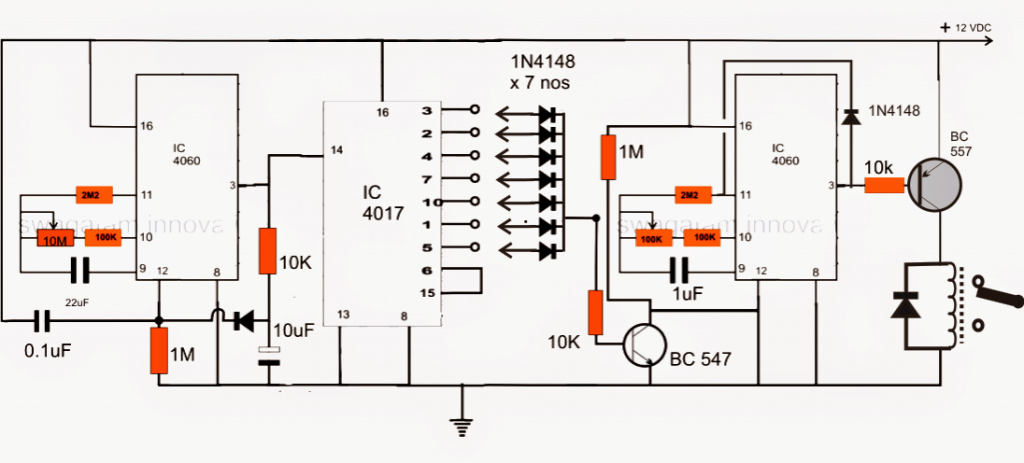

Aj keď medzi BJT a JFET nájdete značné rozdiely, v skutočnosti existuje niekoľko charakteristík zhody, o ktorých sa bude hovoriť v nasledujúcich diskusiách. Hlavný rozdiel medzi týmito zariadeniami je BJT je zariadenie riadené prúdom, ako je znázornené na obrázku 5.1a, zatiaľ čo tranzistor JFET je zariadením riadeným napätím, ako je to znázornené na obrázku 5.1b.

Zjednodušene povedané, súčasný IC.na obrázku 5.1a je okamžitá funkcia úrovne IB. Pre FET je prúd I funkciou napätia VGSdaná vstupnému obvodu, ako je to znázornené na obrázku 5.1b.

V obidvoch prípadoch bude prúd výstupného obvodu riadený parametrom vstupného obvodu. V jednej situácii úroveň prúdu a v druhej použité napätie.

Rovnako ako npn a pnp pre bipolárne tranzistory, aj tu nájdete n-kanálové a p-kanálové tranzistory s efektom poľa. Mali by ste však pamätať na to, že tranzistor BJT je bipolárne zariadenie s predponou bi-, ktorá naznačuje, že úroveň vedenia je funkciou dvoch nosičov náboja, elektrónov a otvorov.

FET na druhej strane je a unipolárne zariadenie to závisí výlučne od vedenia elektrónov (n-kanál) alebo dier (p-kanál).

Slovné spojenie „efekt poľa“ možno vysvetliť takto: všetci sme si vedomí sily permanentného magnetu priťahovať kovové piliny smerom k magnetu bez akéhokoľvek fyzického kontaktu. Celkom podobným spôsobom vo vnútri FET je elektrické pole vytvárané existujúcimi nábojmi, ktoré ovplyvňujú vodivú cestu výstupného obvodu bez priameho kontaktu medzi riadiacimi a riadenými veličinami. Pravdepodobne jednou z najdôležitejších vlastností FET je jeho vysoká vstupná impedancia.

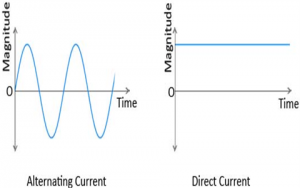

Rozsah od 1 do stovky megohmov výrazne prekonáva rozsahy normálneho vstupného odporu konfigurácií BJT, čo je mimoriadne dôležitý atribút pri vývoji modelov lineárnych zosilňovačov striedavého prúdu.

Avšak BJT nesie väčšiu citlivosť na zmeny vstupného signálu. To znamená, že zmena výstupného prúdu je bežne podstatne vyššia pre BJT ako FET pre rovnaké množstvo zmeny ich vstupných napätí.

Z tohto dôvodu môžu byť štandardné prírastky striedavého napätia pre zosilňovače BJT oveľa vyššie v porovnaní s FET.

Všeobecne povedané, FET sú podstatne tepelne odolnejšie ako BJT a tiež majú často menšiu štruktúru v porovnaní s BJT, vďaka čomu sú špeciálne vhodné na zabudovanie ako integrovaný obvod (IC)lupienky.

Na druhej strane štrukturálne charakteristiky niektorých FET môžu umožniť, aby boli mimoriadne citlivé na fyzické kontakty ako BJT.

Viac vzťahov BJT / JFET

- Pre BJT VBE= 0,7 V je dôležitý faktor pre začatie analýzy jeho konfigurácie.

- Podobne parameter IG= 0 A je obvykle prvá vec, ktorá sa berie do úvahy pri analýze obvodu JFET.

- Pre konfiguráciu BJT somBje často prvým faktorom, ktorý je potrebné určiť.

- Rovnako pre JFET je to obvykle VGS.

V tomto článku sa zameriame na JFET alebo tranzistory s efektom spojovacieho poľa, v nasledujúcom článku sa budeme zaoberať tranzistorom typu kov-oxid-polovodičové pole-efekt alebo MOS-FET.

KONŠTRUKCIA A CHARAKTERISTIKA JFET

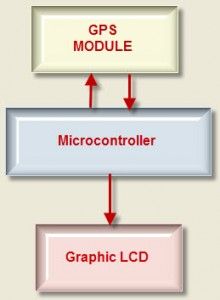

Ako sme sa dozvedeli, slúchadlo JFET má 3 vodiče. Jeden z nich riadi tok prúdu medzi ostatnými dvoma.

Rovnako ako BJT, aj v JFET sa zariadenie s n-kanálom používa výraznejšie ako náprotivky s p-kanálom, pretože n zariadení má tendenciu byť efektívnejšie a užívateľsky prívetivejšie v porovnaní s p-zariadením.

Na nasledujúcom obrázku môžeme vidieť základnú štruktúru alebo konštrukciu n-kanálového JFET. Vidíme, že zloženie typu n tvorí hlavný kanál vo vrstvách typu p.

Horná časť kanála typu n je spojená cez ohmický kontakt s svorkou s názvom odtok (D), zatiaľ čo dolná časť rovnakého kanála je tiež spojená cez ohmický kontakt s iným terminálom s názvom zdroj (S).

Pár materiálov typu p je spojených s terminálom označovaným ako hradlo (G). V podstate zistíme, že odtokové a zdrojové terminály sú spojené s koncami kanálu typu n. Terminál brány je spojený s dvojicou materiálu p-kanála.

Ak na jfet nie je pripojené žiadne napätie, jeho dva spojenia p-n sú bez akýchkoľvek ovplyvňujúcich podmienok. V tejto situácii existuje na každom spoji oblasť vyčerpania, ako je uvedené na obrázku vyššie, ktorá vyzerá celkom ako oblasť diódy p-n bez predpätia.

Vodná analógia

Pracovné a riadiace operácie JFET možno pochopiť pomocou nasledujúcej vodnej analógie.

Tu je možné porovnať tlak vody s veľkosťou aplikovaného napätia od odtoku smerom k zdroju.

Prietok vody sa dá porovnať s prietokom elektrónov. Ústie kohútika napodobňuje zdrojový terminál JFET, zatiaľ čo horná časť kohútika, do ktorej je vháňaná voda, zobrazuje odtok JFET.

Ovládací gombík funguje ako brána JFET. Pomocou vstupného potenciálu riadi tok elektrónov (náboja) z odtoku k zdroju, rovnako ako gombík kohútika riadi tok vody na otvorení úst.

Zo štruktúry JFET vidíme, že odtokové a zdrojové terminály sú na opačných koncoch n-kanála, a keďže tento termín je založený na toku elektrónov, môžeme napísať:

V.GS= 0 V, VDSNejaká pozitívna hodnota

Na obrázku 5.4 môžeme vidieť kladné napätie VDSaplikovaný cez n-kanál. Terminál brány je priamo spojený so zdrojom, aby sa vytvorila podmienka V.GS= 0V. To umožňuje, aby hradlo a zdrojové terminály boli na rovnakom potenciáli, a vedie to k oblasti vyčerpania dolného konca každého p-materiálu, presne tak, ako to vidíme na prvom diagrame vyššie, s podmienkou bez predpätia.

Len čo napätie VDD(= VDS), elektróny sa priťahujú k odtokovému terminálu a generujú konvenčný tok prúdu ID, ako je znázornené na obr. 5.4.

Smer toku náboja ukazuje, že odtokový a zdrojový prúd sú rovnako veľké (ID= JaS). Podľa podmienok znázornených na obrázku 5.4, tok náplne vyzerá celkom neobmedzene a ovplyvňuje ho iba odpor n-kanála medzi odtokom a zdrojom.

Môžete si všimnúť, že oblasť vyčerpania je väčšia okolo hornej časti obidvoch materiálov typu p. Tento rozdiel vo veľkosti regiónu je ideálne vysvetliť na obrázku 5.5. Poďme si predstaviť, že by sme mali v kanáli n jednotný odpor, ktorý by sa dal rozdeliť na úseky uvedené na obr. 5.5.

Súčasný IDmôže vytvárať rozsahy napätia cez kanál, ako je uvedené na rovnakom obrázku. Výsledkom bude, že horná oblasť materiálu typu p bude spätne predpätá o úroveň okolo 1,5 V, pričom dolná oblasť bude iba spätne predpätá o 0,5 V.

Bod, v ktorom je križovatka p-n reverzne predpätý pozdĺž celého kanála, vedie k vzniku hradlového prúdu s nulovými ampérmi, ako je zobrazené na rovnakom obrázku. Táto vlastnosť, ktorá vedie k IG= 0 A je dôležitou charakteristikou JFET.

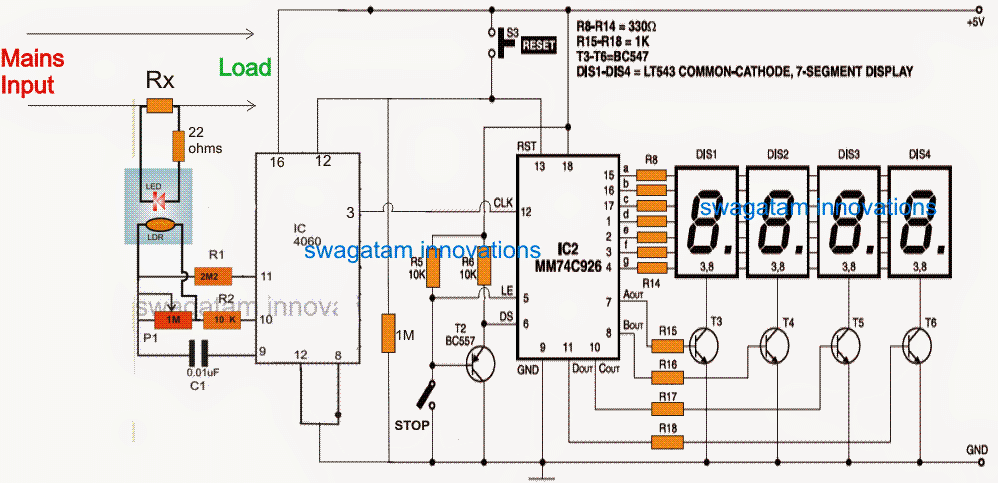

Ako VDSpotenciál sa zvyšuje z 0 na niekoľko voltov, prúd sa zvyšuje podľa Ohmovho zákona a grafu I.Driadok 5DSmôže vyzerať ako preukázané na obr. 5.6.

Porovnávacia priamosť vykreslenia ukazuje, že pre oblasti s nízkou hodnotou VDS, odpor je v podstate rovnomerný. Ako VDSstúpa a blíži sa k úrovni známej ako VP na obrázku 5.6, oblasti vyčerpania sa rozširujú, ako je uvedené na obrázku 5.4.

To má za následok zjavné zníženie šírky kanála. Znížená vodivá cesta vedie k zvýšeniu odporu, čo vedie k krivke na obrázku 5.6.

Čím je krivka vodorovnejšia, tým vyšší je odpor, čo naznačuje, že odpor sa v horizontálnej oblasti blíži k „nekonečným“ ohmom. Keď sa VDSzvyšuje sa do tej miery, že by sa mohlo zdať, že by sa obidve oblasti vyčerpania mohli „kontaktovať“, ako je to znázornené na obr. 5.7, čo vedie k situácii známej ako pinch-off.

Suma, o ktorú sa VDStáto situácia sa nazýva pinch-off napätie a symbolizuje ho VPako je znázornené na obr. 5.6. Slovo pinch-off je vo všeobecnosti zavádzajúce, pretože implikuje súčasné IDje „odštiepený“ a klesne na 0 A. Ako je dokázané na obrázku 5.6, v tomto prípade to vyzerá ťažko. JaDzachováva si úroveň nasýtenia charakterizovanú ako IDSSna obr. 5.6.

Pravda je, že naďalej existuje veľmi málo kanálov s prúdom výrazne vysokej koncentrácie.

Bod, v ktorom ID neklesá pinch-off a zachováva úroveň nasýtenia, ako je to znázornené na obr. 5.6, je potvrdená nasledujúcim dôkazom:

Pretože neexistuje žiadny odtokový prúd, vylučuje sa možnosť rôznorodých úrovní potenciálu cez materiál kanála n na určovanie meniacich sa množstiev spätného skreslenia pozdĺž spojenia p-n. Konečným výsledkom bola strata distribúcie oblasti vyčerpania, ktorá sa spustila pinch-off začať.

Keď zvyšujeme VDSnad VP, oblasť blízkeho kontaktu, kde sa obidve oblasti vyčerpania stretnú navzájom, sa predĺži pozdĺž kanála. Úroveň ID sa však v zásade nemení.

Teda okamih VDSje vyššia ako Vp, JFET získava charakteristiky zdroja prúdu.

Ako je dokázané na obrázku 5.8, prúd v JFET je určený na ID= JaDSS, ale napätie VDSvyššia ako VP je stanovená pripojenou záťažou.

Výber zápisu IDSS je založený na skutočnosti, že ide o prúd typu Drain to Source, ktorý má skratované spojenie cez bránu k zdroju.

Ďalšie vyšetrovanie nám dáva nasledujúce hodnotenie:

JaDSSje najvyšší odtokový prúd pre JFET a je stanovený podmienkami VGS= 0 V a VDS> | VP |.

Všimnite si, že na obr. 5,6 VGSje 0 V pre úplný úsek krivky. V nasledujúcich častiach sa dozvieme, ako sa ovplyvňujú atribúty na obrázku 5.6 ako úroveň VGSje rozmanitá.

V.GS <0V

Nestálosť aplikovaná cez bránu a zdroj sa označuje ako VGS, ktorý je zodpovedný za riadenie operácií JFET.

Ak si vezmeme príklad BJT, tak ako krivky IC.vs VTOTOsú určené pre rôzne úrovne IB, podobne krivky IDvs VDSpre rôzne úrovne VGSmôžu byť vytvorené pre JFET náprotivok.

Z tohto dôvodu je terminál brány nastavený na trvalý nižší potenciál pod úrovňou potenciálu zdroja.

Podľa obrázku 5.9 nižšie sa na redukované V aplikuje cez svorky brány / zdroja -1VDSúrovni.

Cieľ zaujatosti negatívneho potenciálu VGSje vyvinúť vyčerpané regióny podobné situácii vGS= 0, ale pri výrazne zníženom VDS.

To spôsobí, že brána dosiahne bod nasýtenia s nižšími úrovňami VDSako je znázornené na obr. 5.10 (VGS= -1V).

Zodpovedajúca úroveň nasýtenia pre IDmožno zistiť, že je redukovaný a v skutočnosti klesá len ako VGSsa stáva negatívnejšou.

Na obr. 5.10 môžete jasne vidieť, ako odtrhávacie napätie klesá s parabolickým tvarom ako VGSje čoraz negatívnejšie.

Nakoniec, keď VGS= -Vp, bude dostatočne negatívny na to, aby sa stanovila úroveň saturácie, ktorá je nakoniec 0 mA. Na tejto úrovni je JFET úplne „vypnutý“.

Úroveň VGSčo spôsobuje IDna dosiahnutie 0 mA je charakterizované VGS= VP, kde VPje záporné napätie pre n-kanálové zariadenia a kladné napätie pre p-kanálové JFET.

Bežne nájdete väčšinu údajových listov JFET pinch-off napätie špecifikované ako VGS (vypnuté)namiesto VP.

Oblasť na pravej strane odštiepovacieho lokusu na vyššie uvedenom obrázku je miestom, ktoré sa bežne používa v lineárnych zosilňovačoch na dosiahnutie signálu bez skreslenia. Tento región sa všeobecne nazýva oblasť konštantného prúdu, saturácie alebo lineárneho zosilnenia.

Rezistor riadený napätím

Oblasť, ktorá sa nachádza na ľavej strane miesta odštiepenia na rovnakom obrázku, sa nazýva ohmická oblasť alebo oblasť odporu riadená napätím.

V tejto oblasti môže byť zariadenie v skutočnosti prevádzkované ako variabilný rezistor (napríklad v aplikácii na automatické riadenie zosilnenia), pričom jeho odpor je riadený prostredníctvom použitého potenciálu hradla / zdroja.

Vidíte, že sklon každej z kriviek, ktorý tiež znamená odolnosť JFET pre V voči odtoku / zdrojuDS

Keď zvyšujeme VGS s negatívnym potenciálom, sklon každej krivky sa stáva čoraz viac horizontálnejším a úmerne zvyšuje úroveň odporu.

Sme schopní získať dobrú počiatočnú aproximáciu úrovne odporu vzhľadom na napätie VGS pomocou nasledujúcej rovnice.

p-kanál JFET pracuje

Vnútorné usporiadanie a konštrukcia p-kanálového JFET sú úplne identické s n-kanálovým náprotivkom, až na to, že oblasti materiálov typu p a n sú obrátené, ako je uvedené nižšie:

Smery prúdového toku možno tiež považovať za obrátené spolu so skutočnými polaritami napätia VGS a VDS. V prípade p-kanálového JFET bude kanál obmedzený v reakcii na zvýšenie pozitívneho potenciálu cez bránu / zdroj.

Zápis s dvojitým dolným indexom pre VDSspôsobí záporné napätie pre VDS, ako je znázornené na charakteristikách na obr. 5.12. Tu nájdete IDSSpri 6 mA, zatiaľ čo odtrhávacie napätie pri VGS= + 6 V.

Nenechajte sa zmiasť kvôli prítomnosti znaku mínus pre VDS. Jednoducho to naznačuje, že zdroj nesie vyšší potenciál ako odtok.

Vidíte, že krivky pre vysoké VDSúrovne náhle stúpnu na hodnoty, ktoré vyzerajú neobmedzene. Indikované stúpanie, ktoré je zvislé, symbolizuje situáciu poruchy, čo znamená, že prúd v kanálovom zariadení je v tomto okamihu úplne riadený externými obvodmi.

Aj keď to na obr. 5.10 nie je zrejmé pre n-kanálové zariadenie, môže to byť možnosť pri dostatočne vysokom napätí.

Túto oblasť je možné vylúčiť, ak sa VDS (max.)sa zaznamenáva z údajového listu zariadenia a zariadenie je nakonfigurované tak, aby skutočný VDShodnota je nižšia ako táto zaznamenaná hodnota pre akékoľvek VGS.

Dvojica: Bolo preskúmaných 5 najlepších obvodov zosilňovača 40 Watt Ďalej: Datasheet 2N3055, Pinout, aplikačné obvody