V kombinačných obvodoch sa používajú rôzne logické brány na návrh kódovacieho zariadenia, multiplexora, dekodéra a de-multiplexora. Tieto obvody majú niektoré vlastnosti, napríklad výstup z tohto obvodu závisí hlavne od úrovní, ktoré sú kedykoľvek na vstupných svorkách. Tento obvod neobsahuje žiadnu pamäť. Skorší stav vstupu nemá žiadny vplyv na aktuálny stav tohto obvodu. Vstupy a výstupy kombinačného obvodu sú „n“ č. vstupov & ‘m’ č. výstupov. Niektoré z kombinačných obvodov sú polovičné a úplné sčítače, odčítavače, kódovacie zariadenia, dekodéry, multiplexory a demultiplexory. Tento článok pojednáva o prehľade polovičného a úplného sčítača a jeho práci s tabuľkami pravdy.

Čo je sčítačka?

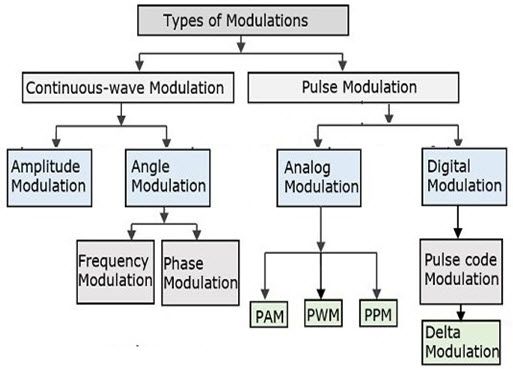

Sčítačka je a digitálny logický obvod v elektronike, ktorá sa vo veľkej miere používa na sčítanie čísel. V mnohých počítačoch a iných typoch procesorov sa pridávače dokonca používajú na výpočet adries a súvisiacich aktivít a na výpočet indexov tabuľky v ALU a dokonca sa používajú v iných častiach procesorov. Môžu byť zostavené pre mnoho číselných zobrazení, ako sú prebytok-3 alebo binárne kódované desatinné miesta. Pridávače sú v zásade rozdelené do dvoch typov: polovičná a úplná.

Čo je obvod sčítačky a sčítačky?

Obvod polovičnej sčítačky má dva vstupy: A a B, ktoré pridávajú dve vstupné číslice a generujú prenos a súčet. Celý obvod sčítačky má tri vstupy: A a C, ktoré pridávajú tri vstupné čísla a generujú prenos a súčet. Tento článok poskytuje podrobné informácie o tom, čo je účelom polovičnej sčítačky a plná sčítačka v tabuľkových formách a dokonca aj v schémach zapojenia. Už bolo spomenuté, že hlavným a rozhodujúcim účelom prídavkov je pridanie. Nižšie sú uvedené podrobné informácie teória polovičnej a úplnej sčítačky.

Základná polovičná a plná sčítačka

Polovica zmija

Keď teda prídeme k scenáru polovičnej sčítačky, pridá dve binárne číslice, kde sa vstupné bity označujú ako augend a addend a výsledkom budú dva výstupy, jeden je súčet a druhý carry. Ak chcete vykonať operáciu súčtu, na oba vstupy sa použije XOR a na obidva vstupy sa použije brána AND, aby sa vytvoril prenos.

Funkčný diagram HA

Zatiaľ čo v obvode úplného sčítača pridáva 3 jednobitové čísla, kde dva z troch bitov možno označiť ako operandy a druhý sa označuje ako bit prenášaný. Vyprodukovaný výstup je 2-bitový a tieto je možné odkazovať ako výstup niesť a súčet.

Pomocou polovičnej sčítačky môžete navrhnúť jednoduché doplnenie pomocou logických brán.

Pozrime sa na príklad pridania dvoch samostatných bitov.

2-bitový polovičná sčítačka pravdy je uvedené nižšie:

Tabuľka pravdy polovičnej sčítačky

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Toto je najmenej možných jednobitových kombinácií. Ale výsledok pre 1 + 1 je 10, celkový výsledok musí byť prepísaný ako 2-bitový výstup. Rovnice teda možno písať ako

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Výstup „1 z 10“ je realizovaný. „SUM“ je normálny výstup a „CARRY“ je uskutočnenie.

Teraz bolo jasné, že 1-bitový sčítač možno ľahko implementovať pomocou brány XOR pre výstup „SUM“ a brány AND pre „nosenie“.

Napríklad, keď potrebujeme pridať dva 8-bitové bajty dokopy, je možné ich implementovať pomocou logického obvodu s úplnou sčítačkou. Polovičná sčítačka je užitočná, ak chcete pridať jednu binárnu číslicu.

Spôsob, ako vyvinúť sčítače dvojbinárnych číslic, by bolo urobiť tabuľku pravdy a zmenšiť ju. Ak chcete vytvoriť sčítač s tromi binárnymi číslicami, operácia sčítania polovice sčítača sa vykoná dvakrát. Podobným spôsobom, keď sa rozhodnete vytvoriť štvorciferný sčítač, sa operácia vykoná ešte raz. S touto teóriou bolo zrejmé, že implementácia je jednoduchá, ale vývoj je časovo náročný proces.

Najjednoduchší výraz používa exkluzívnu funkciu OR:

Súčet = A XOR B

Niesť = A A B

Logický diagram HA

A ekvivalentný výraz v zmysle základných AND, OR a NOT je:

SUM = A.B + A.B ‘

Kód VHDL pre polovičnú sčítačku

Subjekt ha je

Port (a: v STD_LOGIC

b: v STD_LOGIC

sha: out STD_LOGIC

cha: out STD_LOGIC)

koniec ha

Architektúra Chovanie vyššie uvedeného obvodu je

začať

ša<= a xor b

č<= a and b

koniec Behaviorálny

IC IC polovičné sčítačky

Implementáciu polovičného sčítača je možné vykonať pomocou vysokorýchlostných integrovaných obvodov digitálnej logiky CMOS, ako je séria 74HCxx, ktorá obsahuje SN74HC08 (7408) a SN74HC86 (7486).

Obmedzenia polovičnej sčítačky

Hlavným dôvodom, prečo nazývať tieto binárne pridávače ako Half Adders, je to, že neexistuje rozsah, ktorý by zahrnul prenosový bit pomocou staršieho bitu. Toto je teda hlavné obmedzenie HA, ktoré sa kedysi používali ako binárne sčítače, najmä v situáciách v reálnom čase, ktoré zahŕňajú pridanie niekoľkých bitov. Takže toto obmedzenie je možné prekonať použitím úplných doplnkov.

Plná sčítačka

Toto sčítač je ťažké implementovať v porovnaní s polovičným sčítačom.

Celý funkčný diagram sčítača

Rozdiel medzi polovičnou a plnou sčítačkou je ten, že celá sčítačka má tri vstupy a dva výstupy, zatiaľ čo polovičná sčítačka má iba dva vstupy a dva výstupy. Prvé dva vstupy sú A a B a tretí vstup je vstup prenášaný ako C-IN. Keď je navrhnutá logika celého sčítača, spojíte ich osem dohromady, aby ste vytvorili sčítač pre celý bajt a kaskádovali nosný bit z jednej sčítačky do druhej.

Tabuľka pravdy FA

Výstupný prenos je označený ako C-OUT a normálny výstup je reprezentovaný ako S, čo je „SUM“.

S vyššie uvedeným úplná tabuľka pravdy sčítača , je implementácia celého obvodu sčítačky ľahko pochopiteľná. SUM „S“ sa vyrába v dvoch krokoch:

- XORingom poskytnuté vstupy „A“ a „B“

- Výsledok A XOR B sa potom XOR porovná s C-IN

Toto generuje SUM a C-OUT je pravdivý, iba ak sú dva alebo tri vstupy VYSOKÉ, potom bude C-OUT VYSOKÝ. Takže môžeme implementovať celý obvod sčítačky pomocou dvoch obvodov sčítačky. Spočiatku sa polovičná sčítačka použije na pridanie A a B na vytvorenie čiastočného súčtu a logika sčítača druhej polovice sa môže použiť na pridanie C-IN k súčtu vyprodukovanému sčítačkou prvej polovice na získanie konečného výstupu S.

Ak ktorákoľvek z polovičných sčítacích logík vyprodukuje prenos, dôjde k výstupnému prenosu. Takže C-OUT bude funkciou ALEBO výstupov prenášača polovičnej sčítačky. Ďalej sa pozrite na implementáciu celého obvodu sčítačky.

Logický diagram celého sčítača

Implementácia väčších logických diagramov je možná s vyššie uvedenou úplnou logikou sčítača a na reprezentáciu operácie sa väčšinou používa jednoduchší symbol. Nižšie je uvedené jednoduchšie schematické znázornenie jednobitového úplného sčítača.

S týmto typom symbolu môžeme pridať dva bity dokopy, pričom vezmeme niesť z najbližšieho nižšieho rádu a odošleme niesť do najbližšieho vyššieho rádu. V počítači pre viacbitovú operáciu musí byť každý bit predstavovaný celým sčítačom a musí byť pridaný súčasne. Ak teda chcete pridať dve 8-bitové čísla, budete potrebovať 8 plných sčítačiek, ktoré je možné vytvoriť kaskádovaním dvoch zo 4-bitových blokov.

Polovičné a úplné sčítače pomocou K-Map

Dokonca aj výstupy súčtu a prenosu pre polovičné sčítačky možno získať tiež metódou Karnaughovej mapy (K-mapa). The polovičný a úplný sčítač boolovský výraz možno získať prostredníctvom K-mapy. Ďalej je diskutovaná K-mapa pre tieto doplnky.

Polovičná sčítačka K-mapy je

HA K-mapa

Celá sčítačka K-Map je

FA K-mapa

Logické vyjadrenie SUM a prenosu

Logické vyjadrenie súčtu (S) je možné určiť na základe vstupov uvedených v tabuľke.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ‘+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Logický výraz prenosu (Cout) je možné určiť na základe vstupov uvedených v tabuľke.

= A’B Cin + AB’Cin + AB Cin ‘+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

S vyššie uvedenými tabuľkami pravdy je možné získať výsledky a postup je nasledovný:

Kombinovaný obvod kombinuje rôzne hradla v obvode, kde môžu byť kodér, dekodér, multiplexor a demultiplexor . Vlastnosti kombinačných obvodov sú nasledujúce.

- Výstup v ktoromkoľvek okamihu je založený iba na úrovniach, ktoré sú na vstupných svorkách.

- Nepoužíva žiadnu pamäť. Predchádzajúci stav vstupu nemá žiadny vplyv na súčasný stav obvodu.

- Môže mať ľubovoľný počet vstupov am počet výstupov.

Kódovanie VHDL

Kódovanie VHDL pre celú sčítačku zahrňte nasledujúce.

entita full_add je

Port (a: v STD_LOGIC

b: v STD_LOGIC

cin: v STD_LOGIC

suma: out STD_LOGIC

cout: out STD_LOGIC)

koniec full_add

Chovanie architektúry full_add je

zložka ha je

Port (a: v STD_LOGIC

b: v STD_LOGIC

sha: out STD_LOGIC

cha: out STD_LOGIC)

koncová zložka

signál s_s, c1, c2: STD_LOGIC

začať

HA1: mapa prístavov ha (a, b, s_s, c1)

HA2: mapa prístavov ha (s_s, cin, sum, c2)

náklady<=c1 or c2

koniec Behaviorálny

The rozdiel medzi polovičnou a plnou sčítačkou je to, že polovičná sčítačka produkuje výsledky a celá sčítačka používa polovičnú sčítačku na dosiahnutie iného výsledku. Podobne, zatiaľ čo Full-Adder je z dvoch Half-Adders, Full-Adder je skutočný blok, ktorý používame na vytvorenie aritmetických obvodov.

Noste doplnok Lookahead

V koncepcii obvodov sčítačky hromadného prenosu sú bity, ktoré sú potrebné na doplnenie, okamžite k dispozícii. Zatiaľ čo každá sčítačka si musí nechať čas na príchod carry z predchádzajúceho sčítacieho bloku. Z tohto dôvodu trvá výroba SUM a CARRY viac času, pretože každá sekcia v obvode čaká na príchod vstupu.

Napríklad na doručenie výstupu pre n-tý blok musí prijímať vstup z (n-1) -tého bloku. A toto oneskorenie sa príslušne nazýva oneskorenie šírenia.

Na prekonanie oneskorenia sčítačky zvlnenia sa zaviedla sčítačka so zameraním na hliadky. Tu je možné pomocou komplikovaného hardvéru minimalizovať oneskorenie šírenia. Nasledujúci diagram zobrazuje sčítač nosnej kukly s úplnými doplnkami.

Noste Lookahead pomocou sčítačky

Pravdivostná tabuľka a zodpovedajúce výstupné rovnice sú

| TO | B | C. | C + 1 | Stav |

| 0 | 0 | 0 | 0 | No Carry Generovať |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | No Carry Propagujte sa |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Niesť Generovať |

| 1 | 1 | 1 | 1 |

Rovnica šírenia prenosu je Pi = Ai XOR Bi a generovanie prenosu je Gi = Ai * Bi. S týmito rovnicami možno rovnice súčtu a prenášania reprezentovať ako

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi dodáva prenos iba vtedy, keď sú obidva vstupy Ai a Bi 1, bez ohľadu na prenos vstupov. Pi súvisí s šírením prenosu z Ci na Ci + 1.

Rozdiel medzi polovičnou a plnou sčítačkou

The rozdiel medzi polovičnou a plnou sčítacou tabuľkou je zobrazené nižšie.

| Polovica zmija | Plná sčítačka |

| Half Adder (HA) je kombinačný logický obvod a tento obvod sa používa na pridanie dvoch jednobitových číslic. | Full Adder (FA) je kombinačný obvod a tento obvod sa používa na pridanie troch jednobitových číslic. |

| V HA, akonáhle je prenos vygenerovaný z predchádzajúceho pridania, nemôže byť pridaný do nasledujúceho kroku. | Vo FA, akonáhle je prenos vygenerovaný z predchádzajúceho pridania, môže byť pridaný do nasledujúceho kroku. |

| Polovičná sčítačka obsahuje dve logické brány ako brána AND a brána EX-OR. | Celá sčítačka obsahuje dve brány EX-OR, dve brány OR a dve brány AND. |

| Vstupné bity v polovici sčítača sú dva ako A, B. | Vstupné bity v úplnej sčítačke sú tri ako A, B a C-in |

| Polovičná sčítačka a rovnica prenášania sú S = a⊕b C = a * b | Úplný sčítací logický výraz je S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA sa používa v počítačoch, kalkulačkách, zariadeniach používaných na digitálne meranie atď. | FA sa používa v digitálnych procesoroch, viacnásobné pridávanie bitov atď. |

The kľúčové rozdiely medzi polovičnou a plnou sčítačkou sú diskutované nižšie.

- Polovičná sčítačka generuje súčet a prenos pridaním dvoch binárnych vstupov, zatiaľ čo celá sčítačka sa používa na generovanie súčtu a prenosu pridaním troch binárnych vstupov. Hardvérová architektúra sčítača aj sčítača nie je rovnaká.

- Hlavnou vlastnosťou, ktorá odlišuje HA & FA, je to, že v HA neexistuje žiadna dohoda, ktorá by považovala prenos posledného prírastku za jeho vstup. FA však vyhľadá konkrétny vstupný stĺpec, napríklad Cin, aby zvážil nosný bit posledného prírastku.

- Tieto dva prírastky ukážu rozdiel na základe komponentov použitých v obvode na jeho konštrukciu. Polovičné pridávače (HA) sú navrhnuté kombináciou dvoch logických brán ako AND & EX-OR, zatiaľ čo FA je navrhnutá s kombináciou troch AND, dvoch XOR a jednej brány OR.

- V zásade fungujú HA na 2-dvoch vstupoch s 1 bitom, zatiaľ čo FA fungujú na troch 1-bitových vstupoch. Polovica sčítačky sa používa v rôznych elektronických zariadeniach na vyhodnotenie pridania, zatiaľ čo plná sčítačka sa používa v digitálnych procesoroch na pridanie dlhého bitu.

- Podobnosti v týchto dvoch doplnkoch sú, že HA aj FA sú kombinačné digitálne obvody, takže nepoužívajú žiadny pamäťový prvok, napríklad sekvenčné obvody. Tieto obvody sú nevyhnutné pre aritmetické operácie na zabezpečenie sčítania binárneho čísla.

Plná implementácia sčítača pomocou polovičných sčítačiek

Implementáciu FA je možné vykonať pomocou dvoch polovičných sčítačiek, ktoré sú logicky spojené. Jeho bloková schéma môže byť uvedená nižšie, ktorá informuje o pripojení FA pomocou dvoch polovičných sčítačiek.

Rovnice súčtu a prenášania z predchádzajúcich výpočtov sú

S = A ‘B’ Cin + A ’BC’ v + ABCin

Cout = AB + ACin + BCin

Súčetovú rovnicu je možné zapísať ako.

Cin (A’B „+ AB) + C“ v (A „B + A B“)

Takže Sum = Cin EX-OR (A EX-OR B)

Cin (A EX-ALEBO B) + C’in (A EX-ALEBO B)

= Cin EX-OR (A EX-OR B)

Cout možno písať nasledovne.

COUT = AB + ACin + BCin.

Cout = AB + + sklamanie BCin (A + A)

= ABCin + AB + ACin + A ‘B Cin

= AB (1 + Cin) + ACin + A ‘B Cin

= A B + ACin + A ‘B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ‘B Cin

= AB + AB ‘Cin + A’ B Cin

= AB + Cin (AB ‘+ A’B)

Preto COUT = AB + Cin (A EX-ALEBO B)

V závislosti od vyššie uvedených dvoch rovníc súčtu a prenášania je možné obvod FA implementovať pomocou dvoch HA a brány OR. Schéma zapojenia celej sčítačky s dvoma polovičnými sčítačmi je znázornená vyššie.

Plná sčítačka pomocou dvoch polovičných sčítačiek

Celý dizajn sčítača s využitím brán NAND

Brána NAND je jeden druh univerzálnej brány, ktorá sa používa na vykonávanie akýchkoľvek druhov logických návrhov. Ďalej je uvedený obvod FA so schémou hradiel NAND.

FA pomocou brány NAND

FA je ľahký jednobitový sčítač a ak chceme vykonať pridanie n-bitu, potom n nie. vo formáte kaskádového pripojenia musí byť použitých 1 bitových FA.

Výhody

The výhody polovičnej a plnej sčítačky zahrňte nasledujúce.

- Najdôležitejším účelom polovičnej sčítačky je pridať dve jednobitové čísla

- Plné pridávače majú schopnosť pridať nosný bit, ktorý je výsledkom predchádzajúceho pridania

- S plnou sčítačkou je možné implementovať rozhodujúce obvody ako sčítačka, multiplexor a mnoho ďalších

- Plné obvody sčítačky spotrebúvajú minimálnu energiu

- Výhody úplnej sčítačky oproti polovici sčítačky sú, že plná sčítačka sa používa na prekonanie nevýhody sčítačky s polovičnou sčítačkou, pretože polovica sčítačky sa používa hlavne na pridanie dvoch 1-bitových čísel. Polovica pridávacích bitov nepridáva nosný bit, takže na prekonanie tohto celého sčítača sa pracuje. V Full Adder je možné vykonať pridanie troch bitov a vygeneruje dva výstupy.

- Návrh prídavných zariadení je jednoduchý a je základným stavebným prvkom, aby bolo možné ľahko pochopiť jednobitové pridanie.

- Túto sčítačku je možné previesť na polovičný odčítač pridaním invertora.

- Použitím úplného sčítača je možné dosiahnuť vysoký výkon.

- Vysoká rýchlosť

- Veľmi silné na prispôsobenie napájacieho napätia

Nevýhody

The nevýhody polovičnej a plnej sčítačky zahrňte nasledujúce.

- Polovičná sčítačka navyše nemôže byť použitá pred prenášaním, takže nie je použiteľná na kaskádové pridanie viacbitového.

- Na prekonanie tejto nevýhody je potrebné pridať tri 1-bitové FA.

- Akonáhle sa FA použije vo forme reťazca ako RA (zvlnenie zvlhčovača), potom sa dá znížiť výkonová kapacita pohonu.

Aplikácie

Medzi aplikácie sčítačka s polovičnou a plnou sčítačkou patria nasledujúce aplikácie.

- Sčítanie binárnych bitov je možné vykonať polovičnou sčítačkou pomocou ALU v počítači, pretože používa sčítač.

- Kombináciu polovičnej sčítačky možno použiť na návrh celého obvodu sčítačky.

- Polovičné sčítače sa používajú v kalkulačkách a na meranie adries aj tabuliek

- Tieto obvody sa používajú na zvládnutie rôznych aplikácií v rámci digitálnych obvodov. V budúcnosti bude hrať kľúčovú úlohu v digitálnej elektronike.

- Obvod FA sa používa ako prvok v mnohých veľkých obvodoch, ako napríklad Ripple Carry Adder. Tento sčítač pridáva počet bitov súčasne.

- FA sa používajú v aritmetickej logickej jednotke (ALU)

- FA sa používajú v grafických aplikáciách, ako je GPU (Graphics Processing Unit)

- Používajú sa v multiplikačnom obvode na vykonávanie Carryout Multiplication.

- V počítači sa na generovanie adresy pamäte a na vytvorenie kontrapunktu programu voči nasledujúcej inštrukcii používa aritmetická logická jednotka pomocou funkcie Full Adders.

Teda vždy, keď sa uskutoční sčítanie dvoch binárnych čísel, potom sa číslice spočiatku spočítajú s najmenšími bitmi. Tento proces je možné vykonať pomocou polovičnej sčítačky, pretože je to najjednoduchšie n / w, ktoré umožňuje pridať dve 1-bitové čísla. Vstupy tohto sčítača sú binárne číslice, zatiaľ čo výstupy sú súčet (S) a prenos (C).

Kedykoľvek je zahrnutý počet číslic, potom sa sieť HA použije na jednoduché spojenie najmenších číslic, pretože HA nemôže pridať prenosové číslo zo staršej triedy. Celý sčítač možno definovať ako základ všetkých digitálnych aritmetických zariadení. Používa sa na pridanie troch jednociferných čísel. Tento sčítač obsahuje tri vstupy ako A, B a Cin, zatiaľ čo výstupy sú Sum a Cout.

Súvisiace koncepty

The koncepty súvisiace s polovičnou a plnou sčítačkou len sa nedržať jediného účelu. Majú rozsiahle použitie v mnohých aplikáciách a je spomenutých niekoľko súvisiacich:

- Polovičné a úplné sčítacie číslo IC

- Vývoj 8-bitového sčítača

- Aké sú bezpečnostné opatrenia pre polovičné sčítačky?

- JAVA Applet zvlňovača

Preto je to všetko o teória polovičnej a úplnej sčítačky spolu s pravdivostnými tabuľkami a logickými diagramami je tiež zobrazený návrh úplného sčítača s použitím obvodu sčítača s polovicou. Mnoho z polovičná sčítačka a plná sčítačka pdf k dispozícii sú dokumenty, ktoré poskytujú podrobné informácie o týchto konceptoch. Ďalej je dôležité vedieť ako sa implementuje 4-bitová plná sčítačka ?