ECL (emitter coupled logic) prvýkrát vynašiel v IBM v auguste 1956 Hannon S. Yourke. Táto logika je známa aj ako logika aktuálneho režimu, používaná v počítačoch IBM 7090 a 7094. Rodina ECL je veľmi rýchla v porovnaní s digitálna logika rodiny. Vo všeobecnosti táto logická rodina poskytuje oneskorenie šírenia menšie ako 1 ns. Ide o logickú rodinu založenú na bipolárnych tranzistoroch. Je to najrýchlejší logický rodinný obvod, ktorý je dostupný pre návrh konvenčného logického systému. Tento článok pojednáva o prehľade an emitorový spojený logický obvod , práca s aplikáciami.

Čo je to Emitter Coupled Logic?

Logika spojená s emitorom je najlepšia BJT -založená logická rodina používaná v konvenčnom návrhu logického systému. Niekedy sa nazýva aj logika aktuálneho režimu, čo je veľmi vysokorýchlostná digitálna technológia. Vo všeobecnosti sa ECL považuje za najrýchlejší logický IC, kde dosahuje svoju vysokorýchlostnú prevádzku pomocou veľmi malého kolísania napätia a tiež zabránením vstupu tranzistorov do oblasti saturácie.

Implementácia ECL využíva kladné napájacie napätie, ktoré je známe ako PECL alebo ECL s kladnou referenciou. V skorých ECL bránach sa používa záporné napätie kvôli odolnosti voči šumu. Potom sa ECL s pozitívnymi referenciami stalo veľmi známym vďaka svojim kompatibilnejším logickým úrovniam v porovnaní s logickými rodinami TTL.

Emitorovo viazaná logika rozptýli obrovské množstvo statickej energie, avšak jej celková spotreba prúdu je v porovnaní s CMOS pri vysokých frekvenciách. ECL je teda prospešné hlavne v obvodoch distribúcie hodín a aplikáciách založených na vysokých frekvenciách.

Logické funkcie spojené s emitorom

Vďaka vlastnostiam ECL sa budú používať v mnohých aplikáciách založených na vysokom výkone.

- ECL poskytuje dva výstupy, ktoré sa vždy navzájom dopĺňajú, pretože činnosť obvodu je založená na diferenciálnom zosilňovači.

- Táto logická rodina je vhodná hlavne pre monolitické výrobné metódy, pretože logické úrovne sú funkciou pomerov odporov.

- Zariadenia rodiny ECL generujú správny a doplnkový výstup navrhovanej funkcie bez použitia akýchkoľvek vonkajších meničov. V dôsledku toho znižuje počet balíkov a požiadavky na energiu a tiež znižuje problémy vznikajúce z časových oneskorení.

- Zariadenia ECL v dizajne diferenciálneho zosilňovača ponúkajú širokú flexibilitu výkonu, takže obvody ECL umožňujú použitie ako digitálne, tak aj lineárne obvody.

- Konštrukcia brány ECL má normálne vysokú a nízku vstupnú impedanciu, čo mimoriadne prispieva k dosiahnutiu veľkého ventilátora, ako aj schopnosti pohonu.

- Zariadenia ECL generujú konštantný odber prúdu na napájacom zdroji, aby sa zjednodušil návrh napájacieho zdroja.

- Zariadenia ECL vrátane výstupov s otvoreným žiaričom im jednoducho umožňujú zahrnúť kapacitu pohonu prenosovej linky.

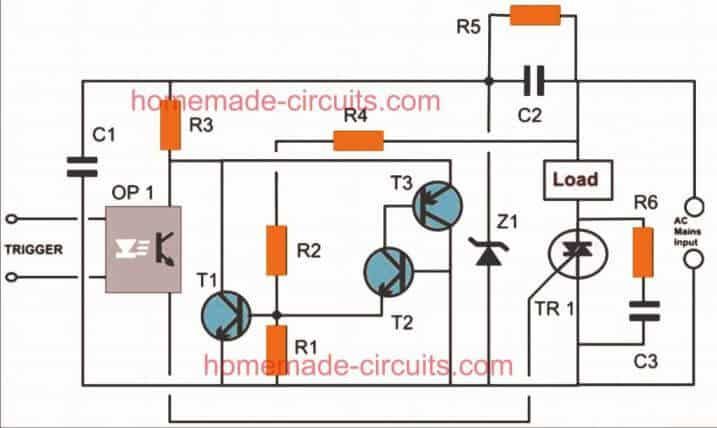

Logický obvod spojený s emitorom

Nižšie je znázornený logický obvod meniča spojený s emitorom, ktorý je navrhnutý s odpormi a tranzistormi. V tomto obvode sú terminály emitorov dvoch tranzistorov jednoducho pripojené k odporu RE obmedzujúceho prúd, ktorý sa používa na zabránenie vstupu tranzistora do saturácie. Tu sa výstup tranzistora odoberá z kolektorového terminálu namiesto emitorového terminálu. Tento obvod poskytuje dva výstupy Vout (invertujúci výstup) a Vout2 (neinvertujúci výstup) a vstupný terminál ako Vin, kde je daný vysoký alebo nízky vstup. +Vcc = 5V.

Ako funguje logika spojená s emitorom?

Činnosť logiky spojenej s emitorom je taká, že kedykoľvek je do obvodu ECL privedený vstup HIGH, potom sa tranzistor „Q1“ zapne a tranzistor Q2 sa vypne, ale tranzistor Q1 nie je nasýtený. Takže to potiahne výstup VOUT2 na HIGH a hodnota výstupu VOUT1 bude NÍZKA kvôli poklesu v rámci R1.

Podobne, keď je hodnota VIN pridelená ECL NÍZKA, potom bude tranzistor Q1 vypnutý a tranzistor Q2 zapnutý. Takže tranzistor Q2 sa nepohne do saturácie. Takže to spôsobí, že výstup VOUT1 bude mať vysokú hodnotu a výstupná hodnota VOUT2 bude nízka kvôli poklesu odporu R2.

Pozrime sa, ako sa tranzistor Q1 a Q2 zapína a vypína, keď je privedené napätie.

Dva tranzistory ako Q1 a Q2 v tomto obvode sú spojené ako diferenciálny zosilňovač rezistorom so spoločným emitorom.

Zdroje napätia pre tento príklad obvodu sú VCC = 5,0, VBB = 4,0 & VEE = 0 V. Vstupné hodnoty HIGH & LOW sú jednoducho definované ako 4,4 V & 3,6 V. V skutočnosti tento obvod generuje LOW výstup & HIGH úrovne, ktoré sú o 0,6 V vyššie; toto je však opravené v rámci skutočných obvodov ECL.

Keď je Vin VYSOKÝ, potom je tranzistor Q1 zapnutý, avšak nie nasýtený a tranzistor Q2 je vypnutý. Takže výstupné napätie ako VOUT2 je ťahané na 5 V cez odpor R2 a dá sa ukázať, že pokles napätia na rezistore R1 je asi 0,8 V, takže VOUT1 = 4,2 V (LOW). Okrem toho VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V, pretože tranzistor Q1 je úplne zapnutý.

Keď je Vin LOW, tranzistor Q2 bude zapnutý, ale nie nasýtený a tranzistor Q1 sa vypne. Preto sa VOUT1 natiahne na 5,0 V pomocou odporu R1 a dá sa ukázať, že VOUT2 je 4,2 V. Tiež VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, keď je tranzistor Q2 zapnutý.

V ECL nie sú dva tranzistory nikdy v saturácii ako t Výkyvy vstupného / výstupného napätia sú pomerne malé, napríklad 0,8 V a vstupná impedancia je vysoká a výstupný odpor je nízky. To pomáha ECL pracovať rýchlejšie s kratším časom oneskorenia šírenia.

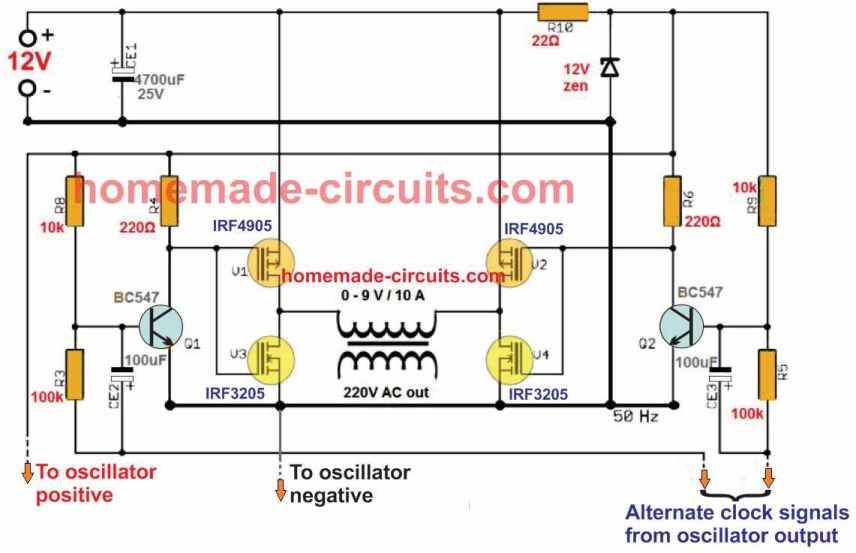

Obvod brány OR/NOR s dvomi vstupmi spojenými s vysielačom

Obvod logického hradla OR/NOR s dvomi vstupmi s emitorom je zobrazený nižšie. Tento obvod je navrhnutý úpravou vyššie uvedeného invertorového obvodu. Úprava spočíva v pridaní ďalšieho tranzistora na vstupnú stranu.

Fungovanie tohto obvodu je veľmi jednoduché. Keď sú vstupy použité na oboch tranzistoroch Q1 a Q2 nízke, výstup 1 (Vout1) sa zmení na hodnotu HIGH. Takže toto Vout1 zodpovedá výstupu brány NOR.

Súčasne, ak je tranzistor Q3 zapnutý, potom druhý výstup (Vout2) bude vysoký. Takže tento výstup Vou2 zodpovedá výstupu brány OR.

Rovnakým spôsobom, ak sú oba vstupy tranzistorov Q1 & Q2 VYSOKÉ, potom sa zapnú tranzistory Q1 a Q2 a poskytne nízky výstup na svorke VOUT1.

Ak je tranzistor Q3 počas tejto operácie vypnutý, potom bude poskytovať vysoký výstup na svorke VOUT2. Takže pravdivostná tabuľka pre bránu OR/NOR je uvedená nižšie.

|

Vstupy |

Vstupy | ALEBO |

NOR |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emitorovo viazané logické charakteristiky

Charakteristiky ECL zahŕňajú nasledujúce.

- V porovnaní s TTL má ECL rýchlejší čas šírenia v rozmedzí od 0,5 do 2 ns. Logický rozptyl energie spojený s emitorom je však vyšší v porovnaní s TTL, napríklad 30 mW.

- Vstupno-výstupné napätie ECL má malý výkyv, napríklad 0,8.

- Vstupná impedancia ECL je vysoká a výstupný odpor je nízky; v dôsledku toho tranzistor mení svoje stavy veľmi rýchlo.

- Kapacita ventilátora ECL je vysoká a oneskorenie brány je nízke.

- O/p logika ECL sa mení zo stavu LOW do stavu HIGH, ale úrovne napätia pre tieto stavy sa budú líšiť medzi TTL a EC.

- Odolnosť proti šumu ECL je 0,4V.

Výhody a nevýhody

The výhody logiky spojenej s emitorom sú diskutované nižšie.

- Fanout ECL je 25, čo je lepšie v porovnaní s TTL a je nízke v porovnaní s CMOS.

- Priemerný čas oneskorenia šírenia ECL je 1 až 4 ns, čo je lepšie v porovnaní s CMOS a

- TTL. Preto sa nazýva najrýchlejšia logická rodina.

- Keď sa BJT v žiariči spoja logické brány pracujú v aktívnej oblasti, potom majú maximálnu rýchlosť v porovnaní so všetkými logickými rodinami.

- ECL brány generujú doplnkové výstupy.

- Prúdové spínacie špičky nie sú v napájacích vodičoch.

- Výstupy môžu byť spojené spoločne, aby poskytovali funkciu káblového OR.

- Parametre ECL sa teplotou príliš nemenia.

- Nie. počet funkcií prístupných z jediného čipu je vysoký.

The nevýhody logiky spojenej s emitorom sú diskutované nižšie.

- Má extrémne nižšiu šumovú rezervu, tj ±200 mV.

- Stratový výkon je vysoký v porovnaní s inými logickými hradlami.

- Na prepojenie s inými logickými rodinami sú potrebné prepínače úrovní.

- Fanout obmedzuje kapacitné zaťaženie.

- V porovnaní s TTL , ECL brány sú drahé.

- V porovnaní s CMOS a TTL je odolnosť proti hluku ECL najhoršia.

Aplikácie

Aplikácie logiky spojenej s emitorom zahŕňajú nasledujúce.

- Logika spojená s emitorom sa používa ako technológia logiky a rozhrania v rámci extrémne vysokorýchlostných komunikačných zariadení, ako sú optické rozhrania transceiverov, siete Ethernet a ATM (Asynchrónny prenosový režim).

- ECL je logická rodina založená na BJT, kde jej vysokorýchlostnú prevádzku možno dosiahnuť použitím relatívne malého kolísania napätia a zabránením pohybu tranzistorov do oblasti saturácie.

- ECL sa používa pri výrobe obvodov ASLT v rámci IBM 360/91.

- ECL sa vyhýba používaniu vrstvených tranzistorov pomocou jednostranného predpätia i/p a kladnej spätnej väzby medzi primárnymi a sekundárnymi tranzistormi na dosiahnutie funkcie invertoru.

- ECL sa používa v extrémne vysokorýchlostnej elektronike.

Teda toto je prehľad logiky spojenej s emitorom alebo ECL – obvod, práca, vlastnosti, charakteristiky a aplikácie. ECL je veľmi najrýchlejšia logická rodina založená na BJT v porovnaní s inými rodinami digitálnych logík. Maximálnu rýchlosť dosahuje použitím malého kolísania napätia a zabránením pohybu tranzistorov do oblasti nasýtenia. Táto logická rodina poskytuje neuveriteľné oneskorenie šírenia 1ns a v najnovších rodinách ECL je toto oneskorenie znížené. Tu je otázka pre vás, aký je alternatívny názov pre ECL?

![Obvod iónového detektora [detektor statického výboja]](https://electronics.jf-parede.pt/img/sensors-and-detectors/09/ion-detector-circuit-static-discharge-detector-1.jpg)