Inštrukčná sada alebo architektúra inštruktážnej sady je štruktúra počítača, ktorá poskytuje príkazy pre počítač, ktoré vedú počítač pri spracovaní údajov. Sada inštrukcií pozostáva z pokynov, režimov adresovania, natívnych dátových typov, registrov, prerušenia, spracovania výnimiek a architektúry pamäte. Inštrukčnú sadu je možné emulovať v softvéri pomocou tlmočníka alebo zabudovať do hardvéru procesora. Architektúru sady inštrukcií možno považovať za hranicu medzi softvérom a hardvérom. Klasifikácia mikrokontrolérov a mikroprocesory je možné vykonať na základe architektúry inštrukčnej sady RISC a CISC.

Inštruktážna sada procesora

Sada inštrukcií špecifikuje funkčnosť procesora vrátane operácií podporovaných procesorom, mechanizmov úložiska procesora a spôsobu kompilácie programov do procesora.

Čo je RISC a CISC?

The RISC a CISC možno rozšíriť nasledovne:

RISC predstavuje počítač so zníženou inštrukčnou sadou a

CISC predstavuje počítač s komplexnou inštrukčnou sadou.

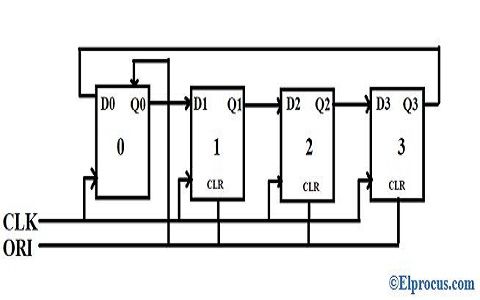

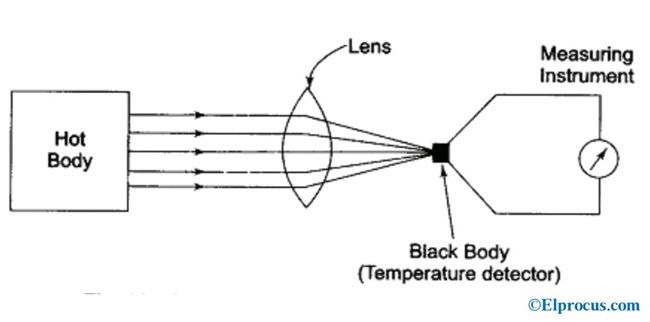

Architektúra RISC (počítač so zníženou sadou inštrukcií)

Architektúra RISC

The architektúra mikrokontroléra ktorý využíva malú a vysoko optimalizovanú sadu pokynov, sa nazýva počítač so zníženou sadou inštrukcií alebo sa jednoducho nazýva RISC. Tiež sa nazýva architektúra LOAD / STORE.

Na konci 70. a začiatkom 80. rokov boli projekty RISC primárne vyvíjané od Stanfordu, UC-Berkley a IBM. John Coke z výskumného tímu IBM vyvinul RISC znížením počtu pokynov potrebných na spracovanie výpočtov rýchlejšie ako v CISC. Architektúra RISC je rýchlejšia a čipy potrebné na výrobu architektúry RISC sú tiež lacnejšie v porovnaní s architektúrou CISC.

Typické vlastnosti architektúry RISC

- Pipeline technika RISC, vykonáva viac častí alebo etáp inštrukcií súčasne tak, aby bola optimalizovaná každá inštrukcia na CPU. Preto majú procesory RISC takt na jeden cyklus, ktorý sa nazýva Vykonanie jedného cyklu.

- Optimalizuje použitie registra s väčším počtom registrov v RISC a väčším počtom interakcií v pamäti je možné zabrániť.

- Jednoduché režimy adresovania, dokonca aj zložité adresovanie je možné vykonať pomocou aritmetiky AND / OR logické operácie .

- Zjednodušuje dizajn kompilátora používaním identických registrov na všeobecné účely, čo umožňuje použitie ľubovoľného registra v akomkoľvek kontexte.

- Pre efektívne využitie registrov a optimalizáciu využitia pipeline je potrebná redukovaná sada inštrukcií.

- Počet bitov použitých pre operačný kód je znížený.

- Spravidla je v RISC 32 alebo viac registrov.

Výhody architektúry procesora RISC

- Kvôli malej množine pokynov RISC môžu prekladače jazykov na vysokej úrovni produkovať efektívnejší kód.

- RISC umožňuje slobodu využitia priestoru na mikroprocesory kvôli svojej jednoduchosti.

- Namiesto použitia Stacku používa veľa procesorov RISC registre na odovzdávanie argumentov a uchovávanie lokálnych premenných.

- Funkcie RISC používajú iba niekoľko parametrov a procesory RISC nemôžu používať pokyny na volanie, a preto používajú pokyny s pevnou dĺžkou, ktoré sa dajú ľahko zreťaziť.

- Môže sa maximalizovať rýchlosť operácie a minimalizovať čas vykonania.

- Je potrebných veľmi malé množstvo formátov inštrukcií (menej ako štyri), niekoľko pokynov (okolo 150) a niekoľko režimov adresovania (menej ako štyri).

Nevýhody architektúry procesora RISC

- S nárastom dĺžky pokynov sa zvyšuje zložitosť vykonávania procesorov RISC z dôvodu ich znakového cyklu na jednu inštrukciu.

- Výkon procesorov RISC závisí väčšinou od kompilátora alebo programátora, pretože znalosti kompilátora zohrávajú pri konverzii kódu CISC na kód RISC dôležitú úlohu, preto kvalita generovaného kódu závisí od kompilátora.

- Pri preplánovaní kódu CISC na kód RISC, ktorý sa označuje ako rozšírenie kódu, dôjde k zväčšeniu jeho veľkosti. Kvalita tohto rozšírenia kódu bude opäť závisieť od kompilátora a tiež od inštrukčnej sady stroja.

- Vyrovnávacia pamäť prvej úrovne procesorov RISC je tiež nevýhodou systému RISC, v ktorom majú tieto procesory veľké pamäte cache na samotnom čipe. Na dodanie pokynov sú veľmi potrebné rýchle pamäťové systémy .

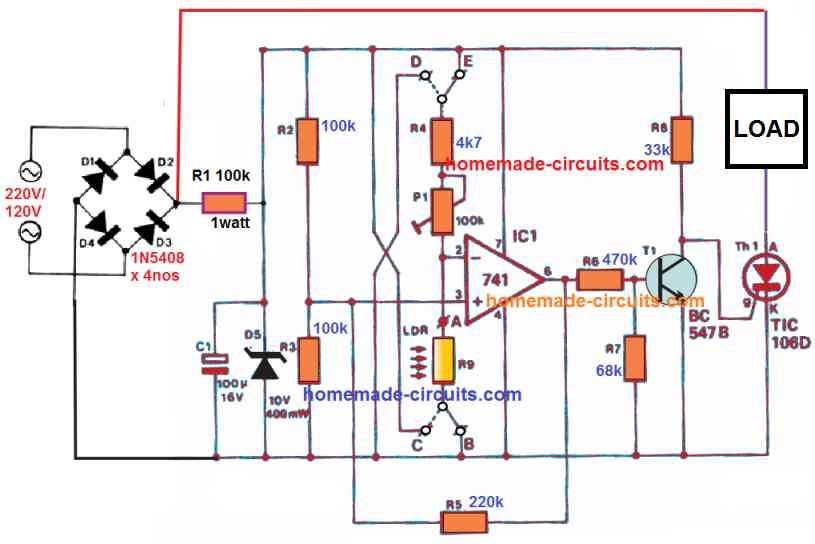

Architektúra CISC (počítač s komplexnou inštrukčnou sadou)

Hlavným zámerom architektúry procesora CISC je dokončiť úlohu použitím menšieho počtu montážnych liniek. Na tento účel je procesor zostavený tak, aby vykonával sériu operácií. Komplexná výučba sa tiež nazýva MULT, ktorá funguje pamäťové banky počítača priamo bez toho, aby kompilátor vykonával funkcie ukladania a načítania.

Architektúra CISC

Vlastnosti architektúry CISC

- Pre zjednodušenie architektúry počítača podporuje CISC mikroprogramovanie.

- CISC má viac preddefinovaných pokynov, ktoré uľahčujú návrh a implementáciu jazykov na vysokej úrovni.

- CISC pozostáva z menšieho počtu registrov a väčšieho počtu režimov adresovania, zvyčajne 5 až 20.

- Procesor CISC trvá vykonanie pokynov rôznym časom cyklu - viachodinové cykly.

- Z dôvodu komplexnej inštrukčnej sady CISC je technika pipelinovania veľmi náročná.

- CISC pozostáva z väčšieho počtu pokynov, zvyčajne od 100 do 250.

- Špeciálne pokyny sa používajú veľmi zriedka.

- S operandami v pamäti sa manipuluje podľa pokynov.

Výhody architektúry CISC

- Každá inštrukcia strojového jazyka je zoskupená do inštrukcie mikrokódu a podľa toho sa vykoná, a potom sa uloží zabudovaná do pamäte hlavného procesora, ktorá sa nazýva implementácia mikrokódu.

- Pretože pamäť mikrokódu je rýchlejšia ako hlavná pamäť, je možné sadu inštrukcií mikrokódu implementovať bez výrazného zníženia rýchlosti oproti implementácii zapojenej do kábla.

- Celú novú sadu inštrukcií je možné spracovať úpravou dizajnu mikroprogramu.

- CISC, počet inštrukcií potrebných na implementáciu programu je možné znížiť vytvorením bohatých inštrukčných sád a dá sa tiež dosiahnuť efektívnejšie využitie pomalej hlavnej pamäte.

- Vďaka množine pokynov, ktorá sa skladá zo všetkých predchádzajúcich pokynov, je mikrokódovanie ľahké.

Nevýhody CISC

- Čas, ktorý rôzne hodiny vykonajú, sa bude líšiť - z tohto dôvodu sa výkon stroja spomalí.

- Zložitosť inštrukčnej sady a hardvéru čipu sa zvyšuje, pretože každá nová verzia procesora pozostáva z podmnožiny starších generácií.

- Iba 20% existujúcich pokynov sa použije v typickej programovacej udalosti, aj keď existuje veľa špecializovaných pokynov, ktoré sa ani často nepoužívajú.

- Podmienené kódy sú nastavené inštrukciami CISC ako vedľajší efekt každej inštrukcie, ktorá si vyžaduje toto nastavenie - a keďže následná inštrukcia zmení bity podmienkových kódov, musí kompilátor predtým, ako k tomu dôjde, preskúmať bity podmienkových kódov.

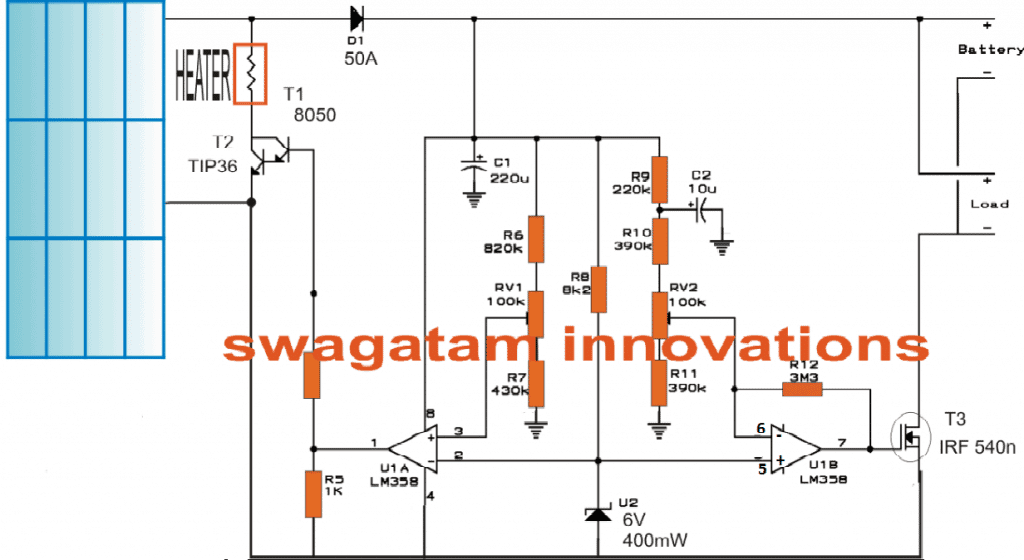

RISC vs. CISC

- Programátorovi môže zabrániť plytvaniu cyklami odstránením nepotrebného kódu z RISC, ale pri použití kódu CISC to vedie k plytvaniu cyklami z dôvodu neefektívnosti CISC.

- V RISC je každá inštrukcia určená na vykonanie malej úlohy, takže na vykonanie zložitej úlohy sa použije viac malých inštrukcií súčasne, zatiaľ čo na vykonanie tej istej úlohy pomocou CISC je potrebných iba niekoľko inštrukcií - pretože je schopná vykonávať zložitú úlohu pretože pokyny sú podobné vysokojazyčnému kódu.

- CISC sa zvyčajne používa pre počítače, zatiaľ čo RISC sa používa pre inteligentné telefóny, tablety a ďalšie elektronické zariadenia.

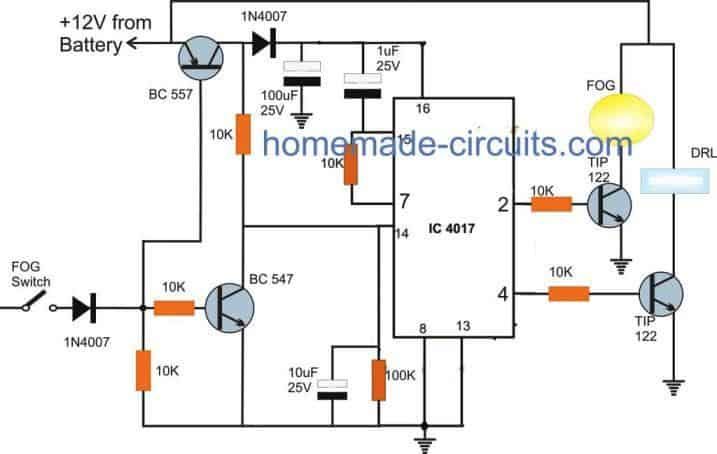

Nasledujúci obrázok ukazuje viac rozdielov medzi RISC a CISC

RISC vs. CISC

Tento článok teda pojednáva o vlastnostiach architektúry RISC a CISC architektúry procesorov RISC a CISC, výhodách a nevýhodách architektúry RISC a CISC a rozdieloch medzi architektúrami RISC a CISC so krátkym nápadom. Ak chcete získať viac informácií o architektúrach RISC a CISC, pošlite svoje dotazy komentárom nižšie.

Fotografické úvery:

- Inštrukčná sada procesora od arstechnica

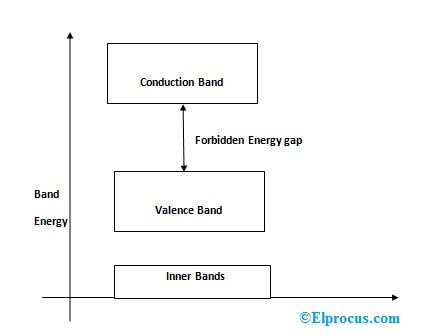

- Architektúra RISC od lsi-sutaz

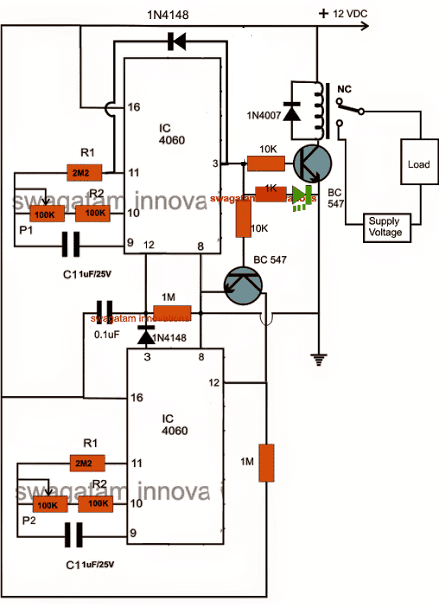

- RISC vs. CISC podľa csarassignment