The fázovo blokovaná slučka je jedným zo základných blokov v moderných elektronických systémoch. Spravidla sa používa v multimédiách, komunikácii a v mnohých ďalších aplikáciách. Existujú dva rôzne typy PLL - lineárne a nelineárne. Nelineárne je ťažké a zložité navrhnúť v reálnom svete, ale teória lineárneho riadenia je dobre modelovaná v analógových PLL. PLL dokázal, že lineárny model je dostatočný pre väčšinu elektronických aplikácií.

Čo je to fázovo blokovaná slučka?

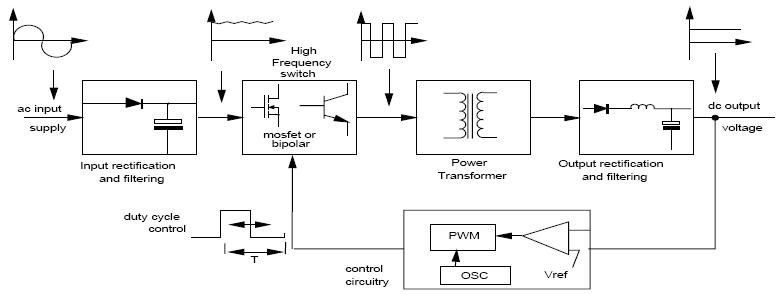

Fázovo blokovaná slučka sa skladá z fázového detektora a napäťovo riadeného oscilátora. Výstupom fázového detektora je vstup napäťovo riadeného oscilátora (VCO) a výstup VCO je pripojený k jednému zo vstupov fázového detektora, ktorý je uvedený nižšie v základnom blokovom diagrame. Keď sa tieto dve zariadenia navzájom napájajú, vytvorí sa slučka.

ZÁKLADNÁ SCHÉMA FÁZY ZABLOKOVANEJ SMYČKY

Bloková schéma a pracovný princíp PLL

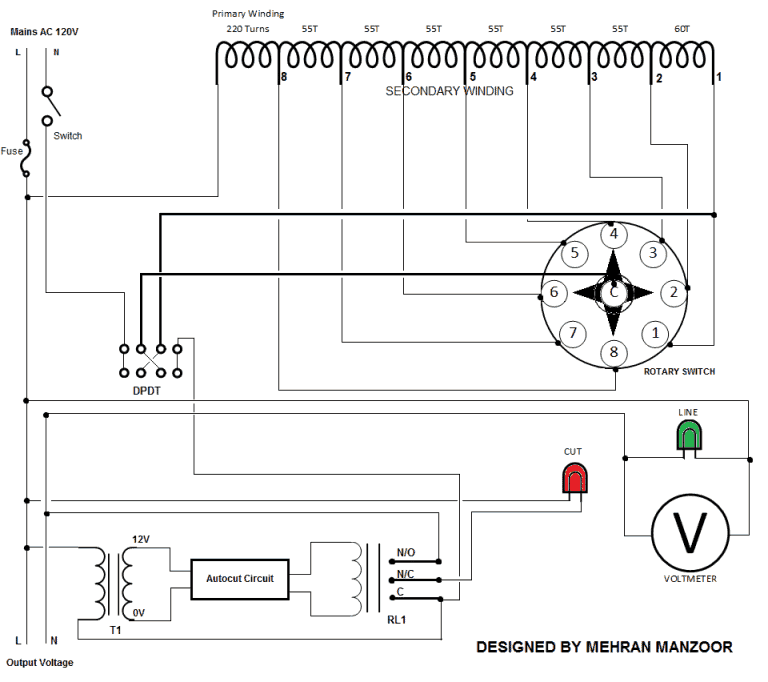

Fázovo blokovaná slučka sa skladá z fázového detektora, a napäťovo riadený oscilátor a medzi nimi je upevnený dolnopriepustný filter. Vstupný signál „Vi“ so vstupnou frekvenciou „Fi“ je povolený fázovým detektorom. V zásade je to fázový detektor komparátor ktorá porovnáva vstupnú frekvenciu fi cez frekvenciu spätnej väzby fo. Výstup fázového detektora je (fi + fo), čo je jednosmerné napätie. Z fázového detektora, t. J. Jednosmerného napätia, sa vstupuje do dolnopriepustného filtra (LPF), odstraňuje vysokofrekvenčný šum a vytvára stabilnú jednosmernú hladinu, tzn. Vf je tiež dynamickou charakteristikou PLL.

Bloková schéma PLL

Výstup dolnopriepustného filtra, t. J. Úroveň jednosmerného prúdu, sa prenáša do VCO. Vstupný signál je priamo úmerný výstupnej frekvencii VCO (fo). Vstupné a výstupné frekvencie sa porovnávajú a upravujú cez spätnoväzbovú slučku, kým sa výstupná frekvencia nerovná vstupnej frekvencii. Preto PLL funguje ako voľný beh, zachytávanie a fázový zámok.

Ak nie je pripojené žiadne vstupné napätie, považuje sa to za fázu s voľným chodom. Akonáhle sa vstupná frekvencia použitá na VOC zmení a vytvorí výstupnú frekvenciu na porovnanie, nazýva sa to fáza zachytenia. Na nasledujúcom obrázku je znázornená bloková schéma PLL.

Fázovo blokovaný detektor slučky

Detektor fázovo uzavretej slučky porovnáva vstupnú frekvenciu a výstupnú frekvenciu VCO a vytvára jednosmerné napätie, ktoré je priamo úmerné fázovému rozlíšeniu týchto dvoch frekvencií. Analógové a digitálne signály sa používajú vo fázovo uzavretej slučke. Väčšina z monolitického PLL integrované obvody používajú analógový fázový detektor a väčšina fázových detektorov je z digitálneho typu. V analógových fázových detektoroch sa bežne používa obvod s dvojitou vyváženou zmesou. Niektoré bežné fázové detektory sú uvedené nižšie:

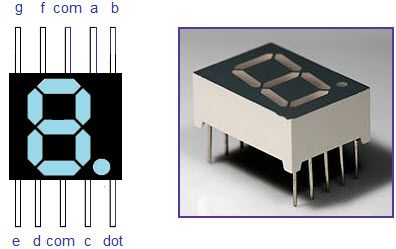

Exkluzívny detektor fázy ALEBO

Exkluzívny fázový detektor OR je typ CMOS IC 4070. Vstupné a výstupné frekvencie sa aplikujú na fázový detektor EX OR. Aby ste dosiahli vysoký výstup, aspoň jeden vstup by mal byť nízky a ostatné podmienky výstupu sú nízke, čo je uvedené v nasledujúcej pravdivej tabuľke. Zoberme do úvahy tvar vlny, vstupné a výstupné frekvencie, t. J. Fi a fo majú fázový rozdiel 0 stupňov. Potom bude výstupné jednosmerné napätie komparátora funkciou fázového rozdielu medzi dvoma vstupmi.

| byť | fo | Vdc |

nízka | nízka | nízka |

nízka | vysoká | vysoká |

vysoká | Nízka | vysoká |

Vysoký | Vysoký | nízka |

Funkcie fázového rozdielu medzi fi a fo sú znázornené v grafe výstupného jednosmerného napätia. Ak je fázový detektor 180 stupňov, potom je výstupné napätie maximálne. Ak sú vstupné aj výstupné frekvencie obdĺžnikové, použije sa tento typ fázových detektorov.

Exkluzívny detektor fázy ALEBO

Detektor fázy spúšťania hrany

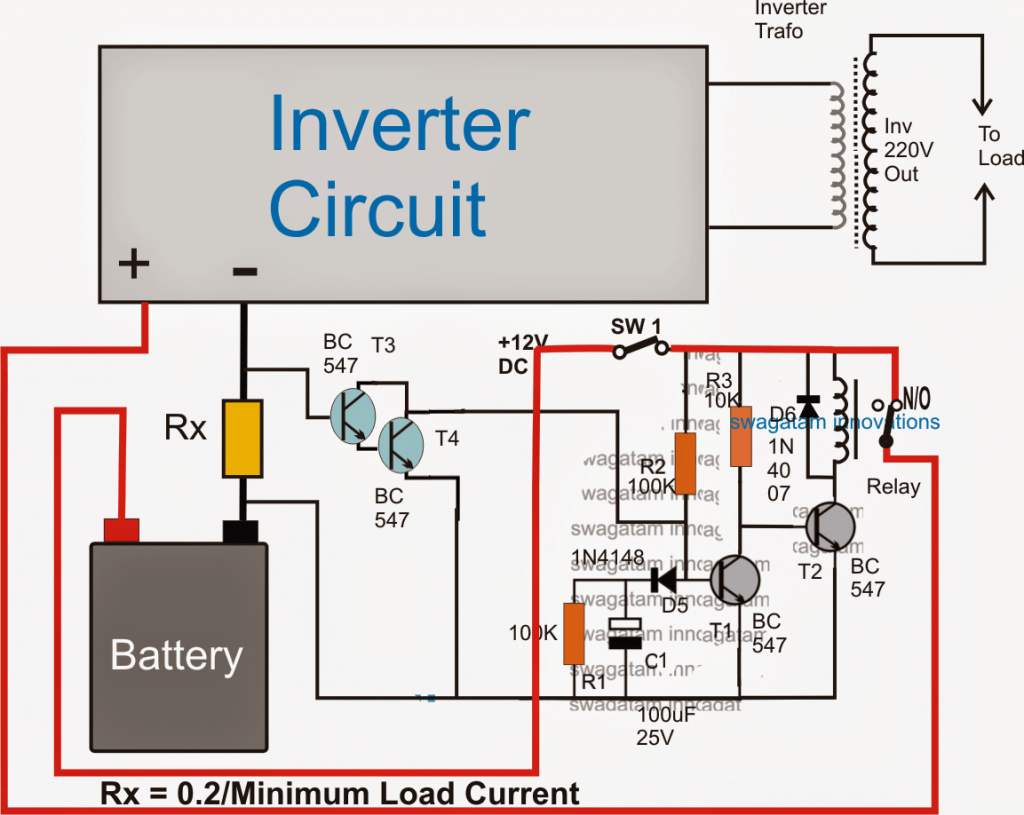

Hranový spúšťací fázový detektor sa používa, keď sú vstupné a výstupné frekvencie v pulznom tvare vlny, ktorý je menší ako 50% pracovný cyklus. Klopný obvod R-S sa používa pre fázové detektory, čo je znázornené na nasledujúcom obrázku. Do z R-S žabky , dve brány NOR sú vzájomne spojené. Výstup fázového detektora môže zmeniť svoj logický stav spustením klopného obvodu R-S. Kladná hrana vstupných a výstupných frekvencií môže meniť výstup fázového detektora.

Detektor fázy spúšťania hrany

Monolitický fázový detektor

Detektor monolitickej fázy je typu CMOS, tj. IC 4044. Je vysoko kompenzovaný harmonickou citlivosťou a problémy s pracovným cyklom sú opustené, pretože obvod môže reagovať iba na prechod vstupného signálu. V kritických aplikáciách je to najviac horúčkový fázový detektor. Nezávislé variácie amplitúdy neobsahujú fázovú chybu, výstupné chybové napätie a pracovný cyklus vstupných kriviek.

Aplikácie fázovo blokovanej slučky

- Demodulačné siete FM pre prevádzku FM

- Používa sa v ovládače otáčok motora a sledovacie filtre.

- Používa sa pri dekódovaní s posunom frekvencie pre demodulačné nosné frekvencie.

- Používa sa včas na digitálne prevodníky.

- Používa sa na potlačenie chvenia, potlačenie zošikmenia, zotavenie hodín.

Toto je všetko o pracovnom a prevádzkovom princípe fázovo uzavretej slučky a jej aplikáciách. Dúfame, že informácie uvedené v článku vám pomôžu dozvedieť sa niečo o projekte a porozumieť mu. Ďalej, ak máte akékoľvek otázky týkajúce sa tohto článku alebo ďalej elektrické a elektronické projekty môžete komentovať v nasledujúcej sekcii. Tu je otázka, aký je najlepší spôsob simulácie PLL pre stabilitu?

Fotografické úvery:

- Bloková schéma PLL obvod dnes

- Exkluzívny detektor fázy ALEBO sanfoundry

- Detektor fázy spúšťania hrany LEARNABOUT-ELECTRONICS