JTAG (Joint Test Action Group) je dobre zavedený štandard IEEE 1149.1, ktorý bol vyvinutý v roku 1980 na riešenie výrobných problémov, ktoré sa vyskytli v elektronických doskách resp. dosky plošných spojov . Táto technológia sa používa na poskytnutie dostatočného testovacieho prístupu pre každú zložitú dosku, keď sa testovací prístup znižoval. Tak bola spustená technológia boundary scan & štandard JTAG resp Špecifikácia JTAG je založená. Zložitosť elektroniky sa každým dňom zvyšuje, takže špecifikácia JTAG sa stala akceptovaným testovacím formátom na testovanie komplikovaných a kompaktných elektronických jednotiek. Tento článok pojednáva o prehľade a JTAG protokol – práca s aplikáciami.

čo je JTAG?

Názov, ktorý je daný štandardnému testovaciemu prístupovému portu IEEE 1149.1, ako aj architektúre Boundary-Scan Architecture, je známy ako JTAG (Joint Test Action Group). Táto architektúra boundary scan sa väčšinou používa v počítači spracovateľov pretože prvý procesor s JTAG vydal Intel. Tento štandard IEEE jednoducho definuje, ako sa testuje obvod počítača, aby sa potvrdilo, či funguje správne po výrobnom procese. Na doskách plošných spojov sa vykonávajú testy na kontrolu spájkovaných spojov.

Joint Test Action Group poskytuje testerom pohľad na piny s každou IC podložkou, čo pomáha pri identifikácii akýchkoľvek porúch na doske plošných spojov. Akonáhle je tento protokol prepojený s čipom, môže pripojiť sondu k čipu tým, že vývojárovi umožní ovládať čip, ako aj jeho spojenia s inými čipmi. Rozhranie so skupinou Joint Test Action môžu vývojári použiť aj na skopírovanie firmvéru do energeticky nezávislej pamäte v elektronickom zariadení.

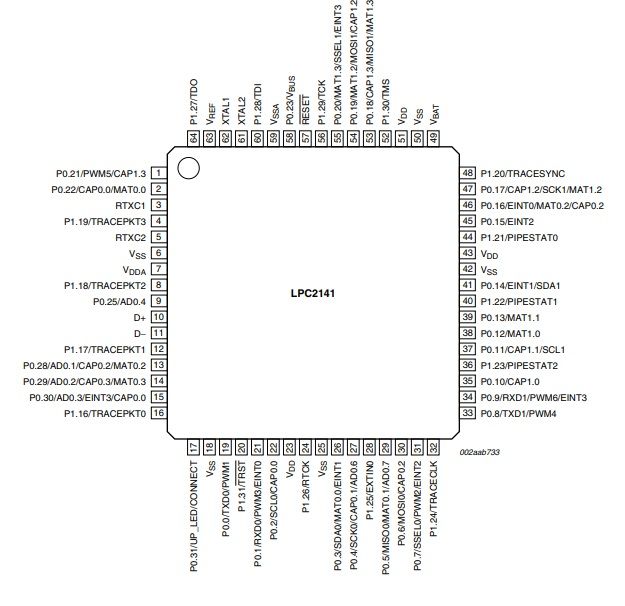

Konfigurácia/Pin Out

Spoločná testovacia akčná skupina obsahuje 20 kolíkov, pričom každý kolík a jeho funkcia sú popísané nižšie.

Pin1 (VTref): Toto je kolík cieľového referenčného napätia, ktorý sa používa na pripojenie k hlavnému zdroju napájania cieľa v rozsahu od 1,5 do 5,0 V jednosmerného prúdu.

Pin2 (napájanie): Toto je cieľové napájacie napätie, ktoré sa používa na pripojenie hlavného zdroja napätia cieľového 1,5VDC – 5,0VDC.

Pin3 (nTRST): Toto je testovací resetovací kolík, ktorý sa používa na resetovanie stavového automatu ovládača TAP.

Piny (4, 6, 8, 10, 12, 14, 16, 18 a 20): Toto sú bežné GND kolíky.

Pin5 (TDI): Toto sú testovacie údaje v kolíku. Tieto údaje sa presunú do cieľového zariadenia. Tento kolík musí byť vytiahnutý za definovaných podmienok na cieľovej doske.

Pin7 (TMS): Toto je kolík stavu testovacieho režimu, ktorý sa vytiahne, aby sa určil ďalší stav stavového stroja ovládača TAP.

Pin9 (TCK): Toto je testovací hodinový kolík, ktorý synchronizuje operácie interného stavového stroja v radiči TAP.

Pin11 (RTCK): Toto je pin Input Return TCK, ktorý sa používa v zariadeniach, ktoré podporujú adaptívne taktovanie.

Pin13 (TDO): Toto je kolík Test Data Out, takže dáta sa presunú z cieľového zariadenia do Flyswatteru.

Pin 15 (nSRST): Toto je kolík resetovania cieľového systému, ktorý je pripojený k hlavnému resetovaciemu signálu cieľa.

Kolíky 17 a 19 (NC): Toto nie sú spojené kolíky.

JTAG funguje

Pôvodné použitie JTAG je na testovanie hraníc. Tu je jednoduchá doska s plošnými spojmi vrátane dvoch integrovaných obvodov, ako sú CPU a FPGA . Typická doska môže obsahovať veľa integrovaných obvodov. Vo všeobecnosti integrované obvody obsahujú veľa kolíkov, ktoré sú spojené s mnohými pripojeniami. V nasledujúcom diagrame sú zobrazené iba štyri pripojenia.

Ak teda navrhujete veľa dosiek, kde každá doska má tisíce pripojení. V tom sú nejaké zlé dosky. Musíme teda skontrolovať, ktorá doska funguje a ktorá nefunguje. Na tento účel bola vytvorená Spoločná testovacia akčná skupina.

Tento protokol môže používať ovládacie kolíky všetkých čipov, ale v nasledujúcom diagrame spoločná testovacia akčná skupina vytvorí všetky výstupné kolíky CPU a všetky vstupné kolíky FPGA. Potom, prenosom určitého množstva údajov z kolíkov CPU a čítaním hodnôt kolíkov z FPGA, JTAG uvádza, že pripojenia dosky plošných spojov sú v poriadku.

Spoločná testovacia akčná skupina v skutočnosti zahŕňa štyri logické signály TDI, TDO, TMS a TCK. A tieto signály musia byť spojené určitým spôsobom. Najprv sú TMS a TCK pripojené paralelne ku všetkým integrovaným obvodom JTAG.

Potom sú TDI a TDO spojené na vytvorenie reťaze. Ako môžete vidieť, každý IC kompatibilný s JTAG obsahuje 4 kolíky, ktoré sa používajú pre JTAG, kde 3 kolíky sú vstupy a 4. kolíky výstup. Piaty kolík ako TRST je voliteľný. Piny JTAG sa zvyčajne nezdieľajú na iné účely.

Použitím spoločnej testovacej akčnej skupiny všetky integrované obvody využívajú hraničné testovanie, ktorého pôvodný dôvod vytvoril JTAG. V súčasnosti sa používanie tohto protokolu rozšírilo, aby umožnilo rôzne veci, ako je konfigurácia FPGA a potom sa JTAG používa v jadre FPGA na účely ladenia.

Architektúra JTAG

Architektúra JTAG je uvedená nižšie. V tejto architektúre sú všetky signály medzi základnou logikou zariadenia a kolíkmi prerušené cez sériovú skenovaciu cestu nazývanú BSR alebo Boundary Scan Register. Tento BSR zahŕňa rôzne „bunky“ hraničného skenovania. Vo všeobecnosti tieto bunky hraničného skenovania nie sú viditeľné, ale možno ich použiť na nastavenie alebo čítanie hodnôt v testovacom režime z kolíkov zariadenia.

Rozhranie JTAG nazývané TAP alebo Test Access Port používa rôzne signály na podporu operácie boundary scan, ako sú TCK, TMS, TDI, TDO a TRST.

- Signál TCK alebo Test Clock jednoducho synchronizuje vnútorné operácie stavového automatu.

- Signál TMS alebo Test Mode Select je vzorkovaný na rastúcej hrane signálu testovacích hodín pre rozhodnutie o ďalšom stave.

- Signál TDI alebo Test Data In označuje posunuté dáta do testovacieho zariadenia inak programovacej logiky. Akonáhle je vnútorný stavový automat v správnom stave, je vzorkovaný na rastúcej hrane TCK.

- Signál TDO alebo Test Data Out označuje posunuté dáta testovacieho zariadenia inak programovacej logiky. Akonáhle je vnútorný stavový automat v správnom stave, potom je platný na klesajúcej hrane TCK

- TRST alebo Test Reset je voliteľný kolík, ktorý sa používa na resetovanie stavového automatu ovládača TAP.

Ovládač TAP

Testovací prístupový bod v architektúre JTAG sa skladá z TAP radiča, registra inštrukcií a registrov testovacích dát. Tento ovládač obsahuje testovací stavový stroj, ktorý je zodpovedný za čítanie signálov TMS a TCK. Dátový i/p kolík sa tu jednoducho používa na načítanie údajov do hraničných buniek medzi jadrom IC a fyzickými kolíkmi a tiež na načítanie údajov do jedného z dátových registrov alebo do registra inštrukcií. Dátový kolík sa používa na čítanie údajov buď z registrov alebo hraničných buniek.

Stavový automat regulátora TAP je riadený TMS a je taktovaný pomocou TCK. Stavový stroj používa dve cesty na označenie dvoch rôznych režimov, ako je inštrukčný režim a dátový režim.

Registre

V rámci boundary scan sú k dispozícii dva druhy registrov. Každé vyhovujúce zariadenie obsahuje minimálne dva alebo viac dátových registrov a jeden inštrukčný register.

Register pokynov

Register inštrukcií sa používa na uchovávanie aktuálnej inštrukcie. Takže jeho údaje používa kontrolér TAP na rozhodnutie, čo má vykonať so získanými signálmi. Údaje registra inštrukcií budú najčastejšie popisovať, do ktorého z údajových registrov musia byť signály odovzdané.

Registre údajov

Dátové registre sú dostupné v troch typoch: BSR (Boundary Scan Register), BYPASS a register ID CODES. Môžu tu byť aj iné dátové registre, ktoré však nie sú potrebné ako prvok štandardu JTAG.

Boundary Scan Register (BSR)

BSR je hlavný testovací dátový register, ktorý sa používa na presun dát z a na I/O kolíky zariadenia.

BYPASS

Bypass je jednobitový register slúžiaci na odovzdávanie údajov z TDI – TDO. To umožňuje testovanie ďalších zariadení v okruhu s minimálnou réžiou.

ID KÓDY

Tento typ dátového registra obsahuje ID kód, ako aj číslo revízie zariadenia. Takže tieto údaje umožňujú pripojenie zariadenia k jeho súboru BSDL (Boundary Scan Description Language). Tento súbor obsahoval podrobnosti o konfigurácii Boundary Scan pre zariadenie.

Fungovanie JTAG je na začiatku zvolený režim inštrukcie, kde jeden zo stavov v tomto režime „cesta“ umožňuje operátorovi hodiny v rámci inštrukcie TDI. Potom sa štátny automat vyvíja, až kým sa nepreskupí. Ďalším krokom pre väčšinu pokynov je výber dátového režimu. Takže v tomto režime sú dáta načítané cez TDI na čítanie z TDO. Pre TDI & TDO budú dátové cesty usporiadané v súlade s inštrukciou, ktorá bola taktovaná. Po dokončení operácie čítania/zápisu sa stavový automat opäť rozvinie do stavu reset.

Rozdiel medzi JTAG a UART

Rozdiel medzi JTAG a UART zahŕňa nasledujúce.

| JTAG |

UART |

| Termín „JTAG“ znamená Joint Test Action Group. | Termín ' UART ” znamená univerzálny asynchrónny prijímač/vysielač. |

| Ide o synchrónne rozhranie, ktoré využíva vstavaný hardvér na programovanie blesku . | UART je asynchrónne rozhranie, ktoré využíva bootloader, ktorý beží v pamäti. |

| Je to sada testovacích portov, ktoré sa používajú na ladenie, ale môžu sa použiť aj na programovanie firmvéru (čo sa bežne robí).

|

UART je typ čipu, ktorý riadi komunikáciu do a zo zariadenia, ako je mikrokontrolér, ROM, RAM atď. Väčšinou ide o sériové pripojenie, ktoré nám umožňuje komunikovať so zariadením. |

| Sú dostupné v štyroch typoch TDI, TDO, TCK, TMS & TRST. | Sú dostupné v dvoch typoch dumb UART & FIFO UART. |

| Joint Test Action Group je sériové programovanie alebo protokol prístupu k dátam, ktorý sa používa pri prepojení mikrokontrolérov a súvisiacich zariadení. | UART je jeden druh čipu, inak subkomponent mikrokontroléra, ktorý sa používa na poskytovanie hardvéru na generovanie asynchrónneho sériového toku, ako je RS-232/RS-485. |

| Komponenty JTAG sú procesory, FPGA, CPLD , atď. | Komponenty UART sú generátor CLK, I/O posuvné registre, vyrovnávacie pamäte pre vysielanie alebo prijímanie, vyrovnávacia pamäť systémovej dátovej zbernice, logika riadenia čítania alebo zápisu atď. |

JTAG protokolový analyzátor

JTAG Protocol Analyzer ako PGY-JTAG-EX-PD je jedným z druhov protokolových analyzátorov, ktorý obsahuje niektoré funkcie na zachytávanie a ladenie komunikácie medzi hostiteľom a testovaným dizajnom. Tento typ analyzátora je popredným nástrojom, ktorý umožňuje testovacím a dizajnérskym inžinierom testovať konkrétne návrhy JTAG pre ich špecifikácie prostredníctvom usporiadania PGY-JTAG-EX-PD ako Master alebo Slave na generovanie JTAG prevádzky a dekódovanie dekódovacích paketov Protokol spoločnej testovacej akčnej skupiny.

Vlastnosti

Funkcie analyzátora protokolu JTAG zahŕňajú nasledujúce.

- Podporuje až 25 MHz frekvencií JTAG.

- Súčasne generuje JTAG prevádzku a dekódovanie protokolu pre zbernicu.

- Má JTAG Master Capability.

- Variabilná rýchlosť dát JTAG a pracovný cyklus.

- Používateľom definované oneskorenia TDI a TCK.

- Rozhranie USB 2.0 alebo 3.0 hostiteľského počítača.

- Analýza chýb v rámci dekódovania protokolu

- Diagram časovania zbernice dekódovaný protokolom.

- Nepretržitý prenos dát protokolu do hostiteľského počítača na poskytovanie veľkej vyrovnávacej pamäte.

- Zoznam aktivít protokolu.

- Pri rôznych rýchlostiach je možné napísať cvičný skript na kombinovanie generovania viacerých dátových rámcov.

Časový diagram

The časový diagram JTAG protokol je uvedený nižšie. V nasledujúcom diagrame zostáva kolík TDO v podmienkach vysokej impedancie s výnimkou stavu ovládača shift-IR/shift-DR.

V podmienkach ovládača shift-IR a Shift-DR sa kolík TDO aktualizuje na klesajúcej hrane TCK cez cieľ a vzorkuje sa na rastúcej hrane TCK cez hostiteľa.

TDI aj TMS kolíky sú jednoducho vzorkované na rastúcej hrane TCK cez Target. Aktualizované na klesajúcom okraji, inak TCK cez hostiteľa.

Aplikácie

The JTAG aplikácie zahŕňajú nasledujúce.

- Spoločná testovacia akčná skupina sa často používa v procesoroch na poskytovanie práva na vstup do ich emulačných alebo ladiacich funkcií.

- Všetky CPLD a FPGA to používajú ako rozhranie na umožnenie prístupu k svojim programovacím funkciám.

- Používa sa na testovanie DPS bez fyzického prístupu

- Používa sa na výrobné testy na úrovni dosiek.

Ide teda o všetko prehľad JTAG – konfigurácia pinov, práca s aplikáciami. Priemyselný štandard JTAG sa používa na overenie návrhu, ako aj testovanie DPS po výrobe. Tu je otázka pre vás, znamená JTAG?