TO digitálno-analógový prevodník ( Dácky , D / A , D2A alebo D-k-A ) je obvod určený na prevod digitálneho vstupného signálu na analógový výstupný signál. Analógovo-digitálny prevodník (ADC) pracuje opačne a transformuje analógový vstupný signál na digitálny výstup.

V tomto článku komplexne diskutujeme o tom, ako fungujú obvody digitálno-analógových a analógovo-digitálnych prevodníkov pomocou schém a vzorcov.

V elektronike môžeme nájsť napätia a prúdy, ktoré sa neustále menia s rôznymi rozsahmi a veľkosťami.

V digitálnych obvodoch je napäťový signál v dvoch formách, buď ako logická vysoká alebo logická nízka logická úroveň, ktoré predstavujú binárne hodnoty 1 alebo 0.

V analógovo-digitálnych prevodníkoch (ADC) je vstupný analógový signál predstavovaný ako digitálna veľkosť, zatiaľ čo digitálno-analógový prevodník (DAC) prevádza digitálnu veľkosť späť na analógový signál.

Ako pracujú digitálno-analógové prevodníky

Proces digitálno-analógovej konverzie je možné uskutočniť mnohými rôznymi technikami.

Jedna známa metóda využíva sieť rezistorov, ktorá sa nazýva rebríková sieť.

Rebríková sieť je navrhnutá tak, aby prijímala vstupy zahŕňajúce binárne hodnoty zvyčajne pri 0 V alebo Vref, a dodáva výstupné napätie ekvivalentné veľkosti binárneho vstupu.

Na nasledujúcom obrázku je znázornená rebríková sieť využívajúca 4 vstupné napätia, ktoré predstavujú 4 bity digitálnych údajov a výstup jednosmerného napätia.

Výstupné napätie je úmerné digitálnej vstupnej hodnote vyjadrenej rovnicou:

Riešením vyššie uvedeného príkladu dostaneme nasledujúce výstupné napätie:

Ako vidíme, digitálny vstup 0110dvaprevedie na analógový výstup 6 V.

Účelom rebríkovej siete je zmena 16 potenciálnych binárnych veličín

cez 0000 až 1111 do jednej zo 16 veličín napätia v intervaloch Vref/ 16.

Preto je možné spracovať viac binárnych vstupov zahrnutím väčšieho počtu jednotiek rebríka a dosiahnuť vyššiu kvantizáciu pre každý krok.

Čo znamená, predpokladajme, že ak použijeme 10-stupňovú rebríkovú sieť, umožní to použitie na zvýšenie množstva krokového napätia alebo rozlíšenia na Vref/dva10alebo Vref/ 1024. V tomto prípade, ak by sme použili referenčné napätie Vref= 10 V by generovalo výstupné napätie v krokoch 10 V / 1024 alebo okolo 10 mV.

Pridanie väčšieho počtu stupňov rebríka nám teda dá proporcionálne vyššie rozlíšenie.

Spravidla pre n počet krokov po rebríku, je to možné vyjadriť pomocou nasledujúceho vzorca:

V.ref/ dvan

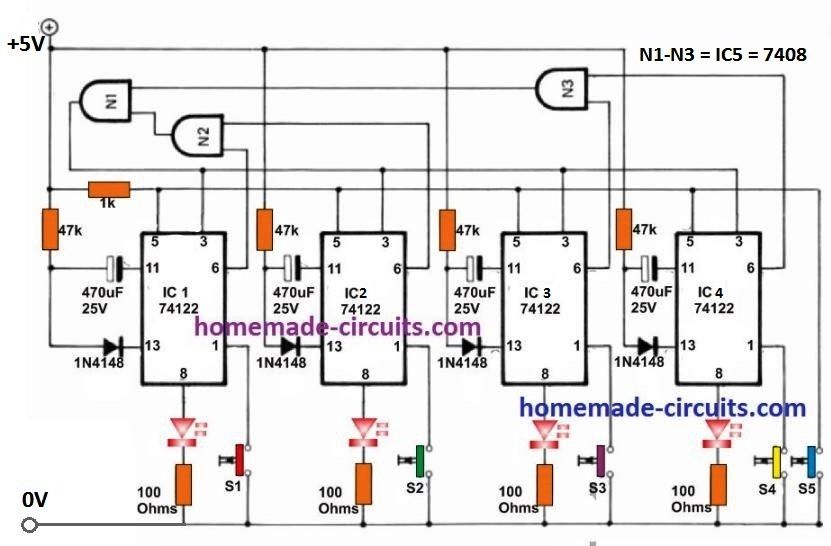

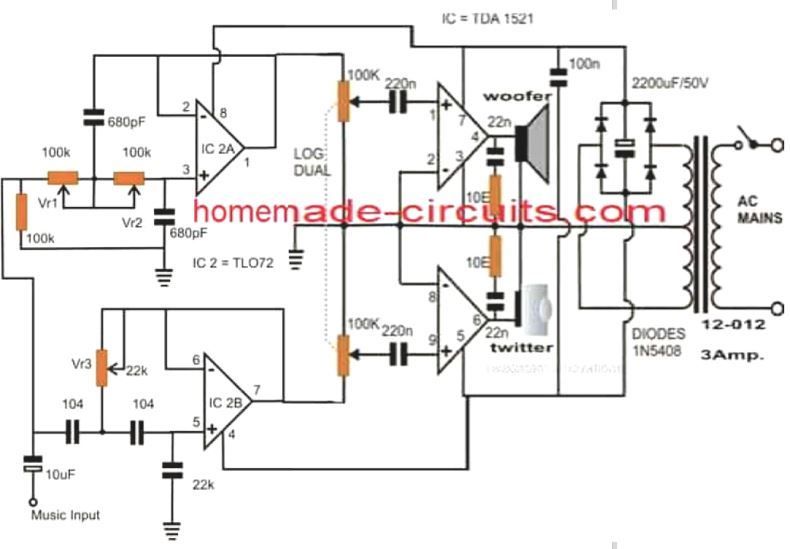

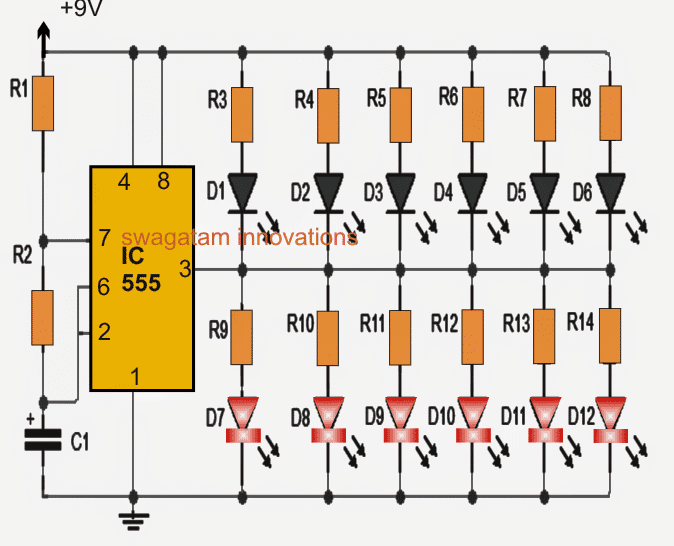

Bloková schéma DAC

Na nasledujúcom obrázku je znázornená bloková schéma štandardného prevodníka DAC využívajúceho rebríkovú sieť označovanú ako rebrík R-2R. Je to vidieť zablokované medzi zdrojom referenčného prúdu a prúdovými spínačmi.

Prúdové spínače sú spojené s binárnymi spínačmi a vytvárajú výstupný prúd úmerný vstupnej binárnej hodnote.

Binárne vstupy prepínajú príslušné nohy rebríka a umožňujú výstupný prúd, ktorý je váženým súčtom aktuálnej referencie.

Ak je to potrebné, k výstupom je možné pripojiť rezistory na interpretáciu výsledku ako analógového výstupu.

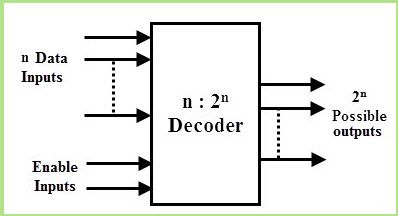

Ako fungujú analógovo-digitálne prevodníky

Doteraz sme diskutovali o tom, ako prevádzať digitálne na analógové signály, poďme sa teraz naučiť, ako postupovať opačne, a to prevádzať analógový signál na digitálny signál. To je možné implementovať pomocou dobre známej metódy nazývanej metóda s dvojitým sklonom .

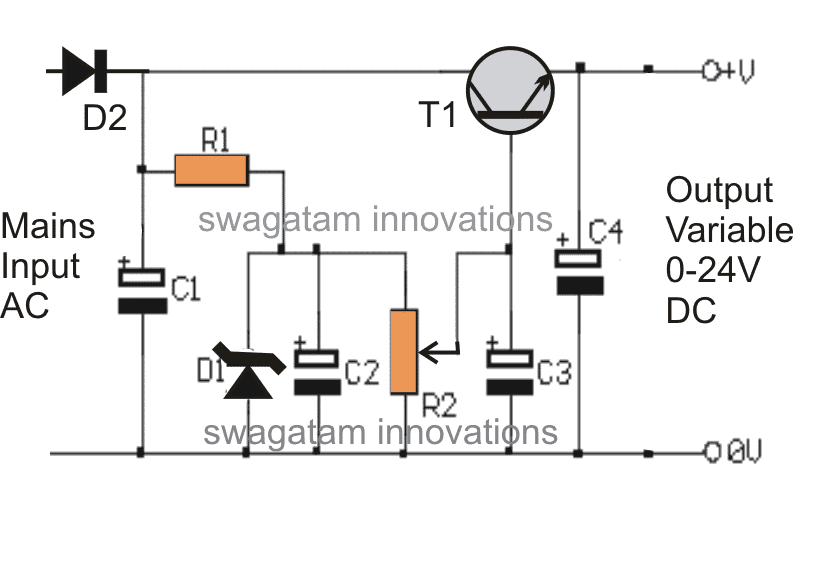

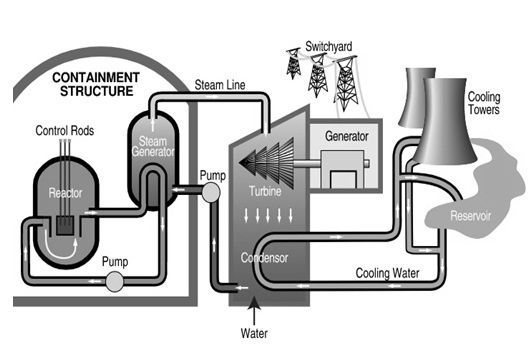

Nasledujúci obrázok zobrazuje blokovú schému štandardného prevodníka ADC s dvojitým sklonom.

Tu sa používa elektronický spínač na prenos požadovaného analógového vstupného signálu na integrátor, ktorý sa tiež nazýva generátor rampy. Tento generátor rampy môže byť vo forme kondenzátora nabitého konštantným prúdom na generovanie lineárnej rampy. Toto produkuje požadovanú digitálnu konverziu cez počítadlo, ktoré pracuje pre kladné aj záporné intervaly sklonu integrátora.

Metóde je možné porozumieť s nasledujúcim popisom:

O pevnom časovom intervale rozhoduje celý merací rozsah počítadla. V tomto intervale vstupné analógové napätie privedené na integrátor spôsobí zvýšenie vstupného napätia komparátora na určitú kladnú úroveň.

S odkazom na časť (b) vyššie uvedeného diagramu ukazuje, že napätie z integrátora na konci pevného časového intervalu je vyššie ako vstupné napätie, ktoré je väčšie.

Po dokončení pevného časového intervalu sa počet nastaví na 0, čo vyzve elektronický spínač na pripojenie integrátora k pevnej referenčnej úrovni vstupného napätia. Potom začne konštantnou rýchlosťou klesať výstup integrátora, ktorý je tiež vstupom kondenzátora.

Počas tohto obdobia čítač neustále napreduje, zatiaľ čo výstup integrátora stále klesá konštantnou rýchlosťou, až kým neklesne pod referenčné napätie komparátora. To spôsobí, že výstup komparátora zmení stav a spustí riadiaci logický stupeň, aby zastavil počítanie.

Uložená digitálna veľkosť vo vnútri počítadla sa stane digitálnym výstupom prevodníka.

Použitie spoločných hodín a integrátora počas kladných aj záporných intervalov sklonu pridáva určitý druh kompenzácie za riadenie driftovania frekvencie hodín a hranice presnosti integrátora.

Je možné škálovať výstup počítadla podľa preferencií používateľa vhodným nastavením referenčnej vstupnej hodnoty a frekvencie hodín. Počítadlo môžeme mať ako binárne, BCD alebo v inom digitálnom formáte, ak je to potrebné.

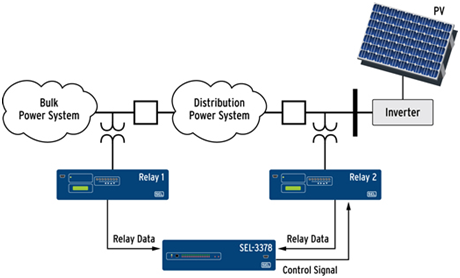

Používanie siete Ladder Network

Metóda rebríkovej siete využívajúca stupne počítadla a komparátora je ďalším ideálnym spôsobom implementácie analógovo-digitálnej konverzie. V tejto metóde začne počítadlo počítať od nuly, ktoré poháňa rebríkovú sieť a generuje stupňovité prírastkové napätie, ktoré pripomína schodisko (pozri obrázok nižšie).

Tento proces umožňuje zvyšovať napätie s každým krokom počítania.

Komparátor monitoruje toto zvyšujúce sa schodiskové napätie a porovnáva ho s analógovým vstupným napätím. Len čo komparátor zaznamená schodiskové napätie nad analógovým vstupom, jeho výstup vyzve na zastavenie počítania.

Hodnota počítadla v tomto bode sa stáva digitálnym ekvivalentom analógového signálu.

Úroveň zmeny napätia generovaného krokmi schodiskového signálu je určená počtom použitých bitov.

Napríklad 12-stupňové počítadlo s referenciou 10 V bude prevádzkovať 10-stupňovú rebríkovú sieť s krokovými napätiami:

V.ref/dva12= 10 V / 4096 = 2,4 mV

Takto sa vytvorí prevodné rozlíšenie 2,4 mV. Čas potrebný na vykonanie prevodu je určený taktovacou frekvenciou počítadla.

Ak sa na prevádzku 12 stupňového počítadla použije takt 1 MHz, maximálny čas potrebný na prevod bude:

4096 x 1 μs = 4096 μs ≈ 4,1 ms

Najmenší možný počet konverzií za sekundu je možné nájsť ako:

č. konverzií = 1 / 4,1 ms ≈ 244 konverzií / sekundu

Faktory, ktoré ovplyvňujú proces premeny

Ak vezmeme do úvahy, že niektorá konverzia môže vyžadovať vyššiu a iná môže vyžadovať kratší čas počítania, môže byť dobrou hodnotou obvykle čas konverzie = 4,1 ms / 2 = 2,05 ms.

Takto sa vytvorí priemerný počet konverzií 2 x 244 = 488.

Pomalší takt by znamenal menej konverzií za sekundu.

Prevodník pracujúci s nižším počtom stupňov počítania (nízke rozlíšenie) by mal vyššiu rýchlosť konverzie.

Presnosť prevodníka je určená presnosťou prevodníka.

Dvojica: Ako vypočítať transformátory s feritovým jadrom Ďalej: Obvod indikátora hladiny paliva v ultrazvuku