Hlavnou nevýhodou kombinačný obvod To znamená, že nepoužíva žiadnu pamäť na uloženie súčasného a predchádzajúceho stavu. Predchádzajúci stav vstupu teda nemá žiadny vplyv na súčasný stav obvodu. Zatiaľ čo sekvenčný obvod má pamäť, takže výstup sa môže líšiť v závislosti od vstupu. Tento typ obvodov využíva predchádzajúci vstup, výstup, hodiny a pamäťový prvok. Tu môžu byť pamäťovými prvkami západky alebo žabky. Sekvenčné obvody sú navrhované rôznymi metódami, ako napríklad pomocou ROM a Flips, PLA, CPLD (komplexné programovateľné logické zariadenie) , FPGA (programovateľné hradlové pole) . V tomto článku budeme diskutovať iba o tom, ako navrhnúť sekvenčný obvod pomocou PLA.

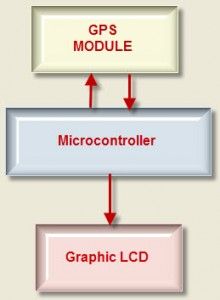

Bloková schéma sekvenčného obvodu, ako je uvedené nižšie:

Bloková schéma postupného obvodu

Návrh sekvenčného obvodu pomocou PLA

Postupné obvody možno realizovať pomocou PLA (Programmable Logic Arrays) a klopných obvodov. V tomto dizajne môže byť priradenie stavu dôležité, pretože použitie priradenia dobrého stavu môže znížiť požadovaný počet výrazov produktu, a tým zmenšiť požadovanú veľkosť PLA. Produktový výraz definovaný ako spojka literálov, kde každý literál je buď premenná, alebo jej negácia.

Uvažujme teda o prevedení kódu. Stavovú tabuľku zobrazenú nižšie v tabuľke je možné realizovať pomocou jednej PLA a troch plážové šľapky ako je zobrazené na obrázku nižšie. Táto konfigurácia obvodu je veľmi podobná konštrukcii založenej na klopných obvodoch ROM, až na to, že ROM je nahradená PLA vhodnej veľkosti. Priradenie stavu vedie k tabuľke pravdivosti uvedenej nižšie. Táto tabuľka by mohla byť uložená v PLA so štyrmi vstupmi, 13 produktovými podmienkami a štyrmi výstupmi, čo by však v porovnaní so 16-slovnou ROM ponúklo málo zmenšenú veľkosť.

| X Q1 Q2 Q3 | S D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabuľka: Tabuľka pravdy

SÚČASNOSŤ ŠTÁT

| ĎALŠÍ ŠTÁT X = 0,1 | SÚČASNOSŤ VÝSTUP (Z) |

| TO | B C | 1 0 |

B C. | D E A E | 1 0 0 1 |

D JE | H H H M | 0 1 1 0 |

H M | A A DO - | 0 1 1 - |

Tabuľka: Tabuľka stavu

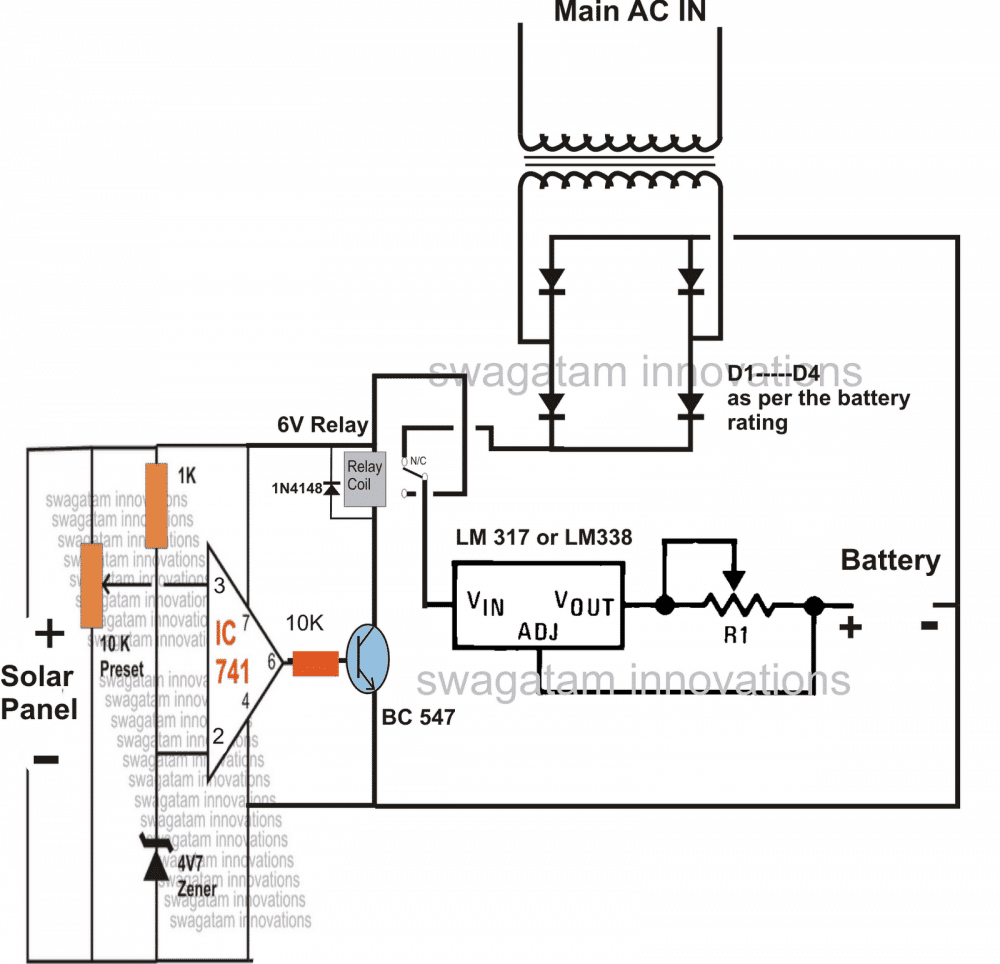

Návrh sekvenčných obvodov pomocou PLA

Rovnice vstupného výstupu odvodené z Karnaughovej mapy

Pretože tu je sedem štátov, sú potrebné tri klopné obvody typu D. Je teda potrebný obvod PLA so 4 vstupmi a 4 výstupmi. Ak sa vezme do úvahy stavové priradenie prevodníka kódu, výslednú výstupnú rovnicu a vstupné klopné rovnice D odvodené od Karnaugha možno napísať nasledujúcimi rovnicami

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | S D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 jedenásť

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Tabuľka PLA, ktorá zodpovedá týmto rovniciam, je uvedená v tabuľke vyššie. Túto tabuľku je možné realizovať pomocou PLA so štyrmi vstupmi, siedmimi produktovými výrazmi a štyrmi výstupmi. Na úvodné overenie činnosti vyššie uvedeného návrhu predpokladajme, že X = 0 a Q1Q2Q3 = 000. Týmto sa v tabuľke vyberú riadky - - 0- a 0 - - -0, takže Z = 0 a D1D2D3 = 100. Po aktívnej časovej hrane Q1Q2Q3 = 100. Ak je ďalší vstup X = 1, potom sú vybraté riadky - - 0 - a - 1- -, takže Z = 0 a D1D2D3 = 110. Po aktívnej časovej hrane Q1Q2Q3 = 110.

Programovateľné logické pole (PLA)

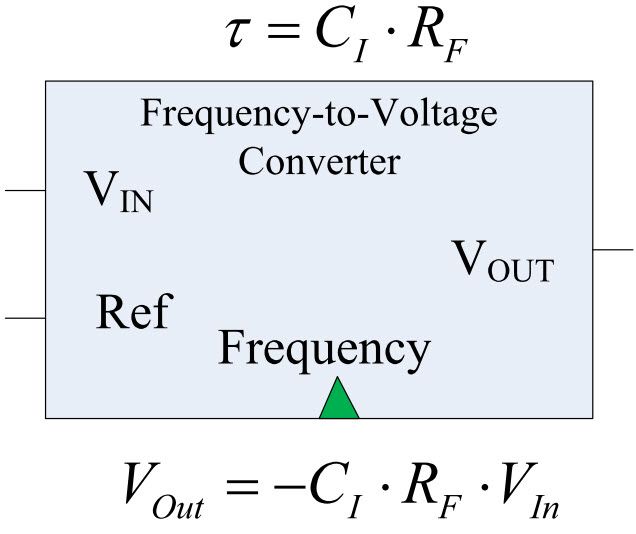

Programmable Logic Array je programovateľné logické zariadenie. Spravidla sa používa na implementáciu kombinačných logických obvodov. PLA má sadu programovateľných rovín AND (pole AND), ktoré odkazujú na množinu programovateľných rovín OR (pole OR), ktoré je potom možné dočasne doplniť, aby vytvorili výstup. Toto rozloženie umožňuje syntetizovať veľké množstvo logických funkcií v systéme Windows súčet produktov (SOP) kanonické formy. Jednoduchá bloková schéma PLA je uvedená nižšie.

Bloková schéma PLA

Hlavný rozdiel medzi PLA a PAL (programovateľná logika poľa) je,

CHKO: Oboje Rovina AND a rovina OR sú programovateľné.

PAL: Programovateľná je iba rovina AND, zatiaľ čo rovina OR je pevná.

Pre lepšie pochopenie PLA tu uvažujeme o nižšie uvedenom príklade.

Pokúsme sa implementovať tieto funkcie f1 a f2 sú uvedené ako

Vstupy x1, x2, x3 a ich príslušné komplementované signály sú dané do programovateľnej roviny AND, kde dostaneme výstupy roviny AND ako mintermy zvané P1, P2, P3. Potom sú tieto signály dané do programovateľnej OR roviny na vytvorenie požadovanej výstupnej funkcie f1 a f2 (súčet výrobkov). Nasledujúci obrázok popisuje implementáciu PLA na úrovni brány pre danú funkcionalitu.

Implementácia CHKO

Toto je všetko o navrhovaní sekvenčných obvodov pomocou PLA. Domnievame sa, že informácie uvedené v tomto článku vám pomôžu lepšie pochopiť tento koncept. Ďalej akékoľvek otázky týkajúce sa tohto článku alebo pomoc v realizácia projektov v oblasti elektrickej energie a elektroniky , môžete nás kontaktovať komentovaním v sekcii komentárov nižšie. Tu je otázka pre vás, Čo sa rozumie pod sekvenčným obvodom?