V tomto príspevku sa naučíme, ako zostaviť logické brány NOT, AND, NAND, OR a NOR pomocou diskrétnych tranzistorov. Hlavnou výhodou použitia tranzistorových logických hradel je, že môžu pracovať aj s napätím 1,5 V.

V niektorých elektronických aplikáciách môže byť dostupné napätie nedostatočné na napájanie TTL alebo dokonca CMOS IC. To platí najmä pre gadgety, ktoré fungujú na batérie. Niet pochýb, že vždy máte možnosť 3-voltového logického integrovaného obvodu. Tieto však nie sú vždy ľahko dostupné pre nadšencov alebo experimentátorov a nefungujú pod ich definovanými napäťovými špecifikáciami (všeobecne pod 2,5 V DC).

Okrem toho môže byť v aplikácii napájanej z batérie miesto len pre jednu 1,5-voltovú batériu. No a čo budeš potom robiť? Zvyčajne IC logické brány by mohli byť nahradené tranzistorovými logickými hradlami. Pre každé jednotlivé logické hradlo je vo všeobecnosti potrebných len pár tranzistorov a pre typickú logiku meniča NOT hradla je potrebný iba jeden tranzistor.

FET verzus bipolárny tranzistor

Tranzistory s efektom poľa (FET) vs bipolárne tranzistory : ktorá je lepšia možnosť pre nízkonapäťové logické obvody? Jedna skvelá vlastnosť FAKTY je, že ich 'zapnutý' odpor je neuveriteľne nízky. Okrem toho potrebujú veľmi nízky prúd pri zapnutí brány.

Pri extrémne nízkonapäťových aplikáciách však majú jedno obmedzenie. Typicky je limit napätia brány jeden volt alebo tak. Okrem toho sa dostupné napätie môže znížiť pod optimálny pracovný rozsah FET, ak je k bráne pripojený odpor obmedzujúci prúd alebo odpor.

Naopak, bipolárne spínacie tranzistory majú výhodu v extrémne nízkonapäťových aplikáciách s jednou batériou, pretože na zapnutie potrebujú iba 0,6 až 0,7 voltov.

Navyše väčšina bežných FET, ktoré sa bežne predávajú v bublinkových baleniach v najbližšom obchode s elektronikou, sú často drahšie ako bipolárne tranzistory. Tiež hromadný balík bipolárnych tranzistorov by sa mohol vo všeobecnosti kúpiť za cenu páru FET.

Manipulácia s FET si vyžaduje podstatne väčšiu starostlivosť ako manipulácia s bipolárnymi tranzistormi. Elektrostatické a všeobecné experimentálne nesprávne použitie spôsobuje, že FET sú obzvlášť náchylné na poškodenie. Spálené komponenty môžu zničiť príjemný, kreatívny večer experimentovania alebo inovácií, netreba zabúdať na emocionálnu bolesť pri ladení.

Základy spínacích tranzistorov

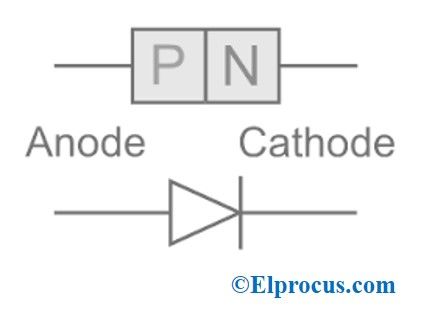

Príklady logických obvodov vysvetlené v tomto článku využívajú bipolárne tranzistory NPN, pretože sú cenovo dostupné a nevyžadujú špeciálnu manipuláciu. Aby ste predišli poškodeniu zariadenia alebo častí, ktoré ho podopierajú, mali by ste pred pripojením obvodu vykonať vhodné bezpečnostné opatrenia.

Aj keď sa naše obvody sústreďujú prevažne na bipolárne tranzistory (BJT), mohli byť rovnako dobre skonštruované pomocou technológie FET.

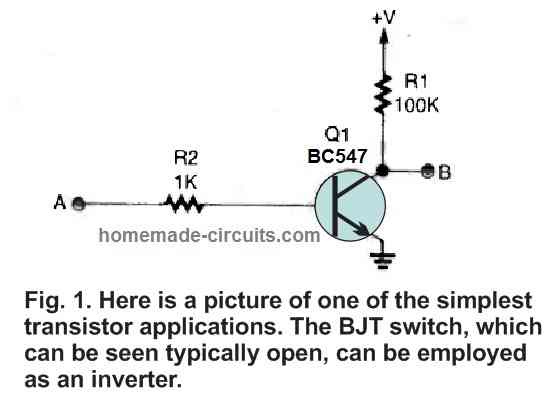

Základný spínací obvod je jednoduchá tranzistorová aplikácia, ktorá je jedným z najjednoduchších návrhov.

Vytvorenie brány NOT s jedným tranzistorom

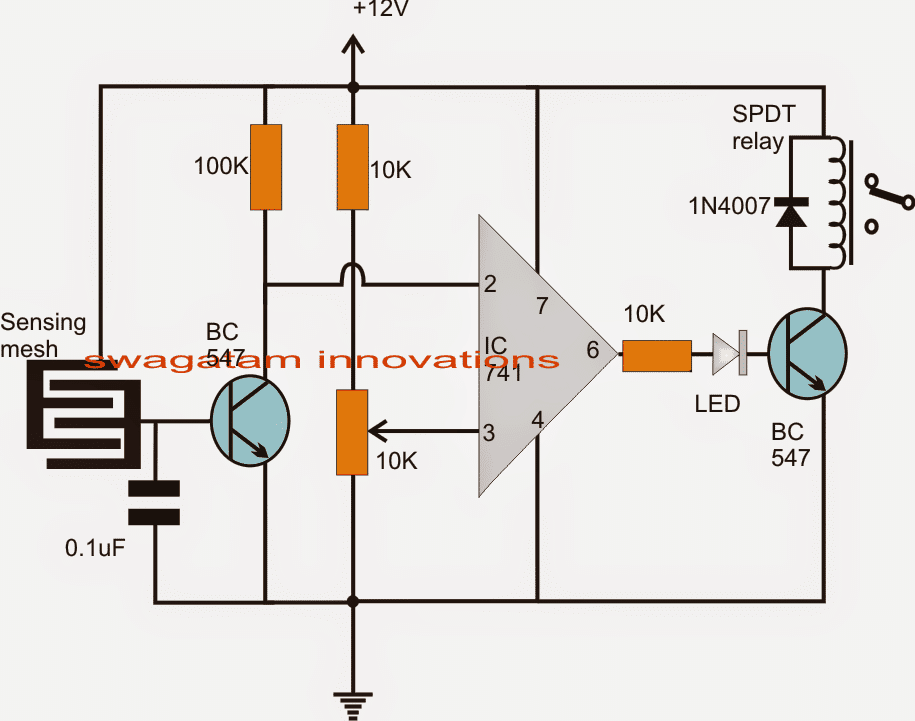

Schéma tranzistorového spínača je znázornená na obrázku 1. V závislosti od toho, ako je implementovaný v konkrétnej aplikácii, môže byť spínač vnímaný buď ako udržiavaný na nízkej úrovni alebo normálne otvorený.

Jednoduché logické hradlo meniča NOT môže byť vytvorené jednoduchým spínacím obvodom znázorneným na obr. 1 (kde bod A je vstup). Hradlo NOT funguje tak, že ak základňa tranzistora (bod A; Q1) nie je predpätá jednosmerným prúdom, zostane vypnutá, čo vedie k vysokej alebo logickej 1 (rovnajúcej sa úrovni V+) na výstupe ( bod B).

Tranzistor sa však aktivuje, keď je do bázy Q1 poskytnuté správne predpätie, čím sa výstup obvodu stlačí na nízku hodnotu alebo na logickú 0 (takmer nulový potenciál). Tranzistor označený ako Q1 je univerzálny bipolárny tranzistor alebo BC547, ktorý sa zvyčajne používa v aplikáciách spínania a zosilňovačov s nízkym výkonom.

Každý tranzistor, ktorý je mu ekvivalentný (napríklad 2N2222, 2N4401 atď.), by fungoval. Hodnoty R1 a R2 boli vybrané tak, aby dosiahli kompromis medzi nízkym odberom prúdu a kompatibilitou. Vo všetkých prevedeniach sú všetky odpory 1/4 watt, 5% jednotiek.

Napájacie napätie je nastaviteľné od 1,4 do 6 V DC. Všimnite si, že obvod môže fungovať ako vyrovnávacia pamäť, keď sú zaťažovací odpor a výstupné pripojenie posunuté na emitor tranzistora.

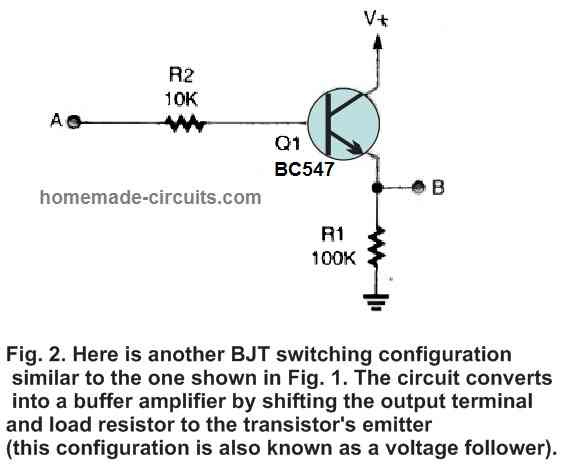

Vytvorenie vyrovnávacej brány pomocou jedného BC547 BJT

Napäťový sledovač alebo vyrovnávací zosilňovač je typ konfigurácie logického spínania identický s konfiguráciou znázornenou na obrázku 2. Treba poznamenať, že zaťažovací odpor a výstupná svorka boli v tomto obvode posunuté z kolektora tranzistora na jeho emitor, čo je hlavný rozdiel medzi týmto dizajnom a dizajnom znázorneným na obr.

Fungovanie tranzistora môže byť tiež 'preklopené' presunutím záťažového odporu a výstupnej svorky na druhý koniec BJT.

Inými slovami, keď nie je poskytnuté žiadne predpätie na vstupe obvodu, výstup obvodu zostáva nízky; ak sa však na vstup obvodu privedie predpätie primeraného napätia, výstup obvodu sa zmení na vysoký. (To je presný opak toho, čo sa deje v predchádzajúcom okruhu.)

Navrhovanie dvojvstupových logických brán pomocou tranzistorov

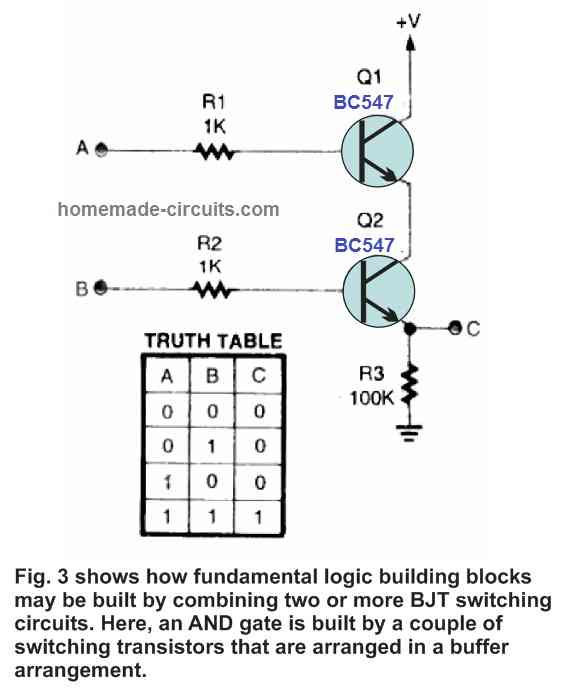

AND Gate pomocou dvoch tranzistorov

Obrázok 3 ilustruje, ako možno vytvoriť základné dvojvstupové AND hradlo pomocou dvojice vyrovnávacích pamätí spolu s pravdivostnou tabuľkou pre toto hradlo. Pravdivostná tabuľka ilustruje, aké by boli výstupné výsledky pre každú odlišnú množinu vstupov. Body A a B sa používajú ako vstupy obvodu a bod C slúži ako výstup obvodu.

Z pravdivostnej tabuľky je dôležité poznamenať, že len jedna sada vstupných parametrov má za následok logický-vysoký výstupný signál, zatiaľ čo všetky ostatné vstupné kombinácie majú za následok logický-nízky výstup. Výstup hradla AND na obrázku 3 zostáva mierne pod V+, keď sa zmení na vysoký.

Stáva sa to kvôli poklesu napätia medzi dvoma tranzistormi (Q1 a Q2).

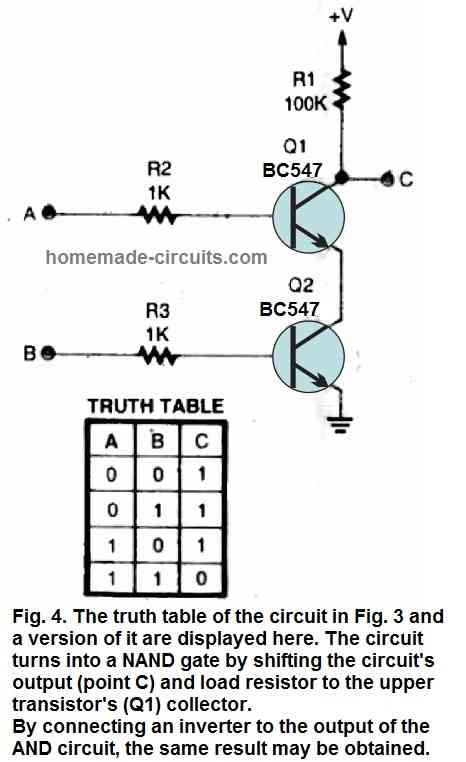

Brána NAND pomocou dvoch tranzistorov

Ďalší variant obvodu na obrázku 3 a súvisiaca pravdivostná tabuľka sú zobrazené na obrázku 4. Obvod sa zmení na hradlo NAND posunutím výstupu (bod C) a výstupného odporu ku kolektoru horného tranzistora (Q1).

Pretože Q1 aj Q2 musia byť zapnuté, aby sa pritiahla spodná strana R1 k zemi, strata napätia na výstupe C je zanedbateľná.

Ak hradla tranzistorového AND alebo tranzistorového NAND hradla potrebujú viac ako dva vstupy, v zobrazených konštrukciách by bolo možné pripojiť viac tranzistorov, aby sa zabezpečili tri, štyri atď. vstupné hradla AND alebo NAND.

Aby sa však kompenzovali straty napätia jednotlivých tranzistorov, malo by sa zodpovedajúcim spôsobom zvýšiť V+.

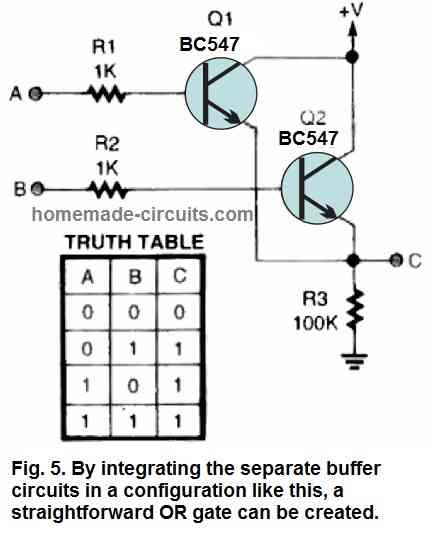

ALEBO Brána pomocou dvoch tranzistorov

Ďalšiu formu logického obvodu s dvoma vstupmi je možné vidieť na obrázku 5 spolu s pravdivostnou tabuľkou obvodu OR-gate.

Výstup obvodu je vysoký, keď je buď vstup A alebo vstup B stlačený vysoko, avšak v dôsledku kaskádových tranzistorov je pokles napätia viac ako 0,5 voltu. Zobrazené čísla opäť ukazujú, že je dostatok napätia a prúdu na ovládanie nasledujúceho hradla tranzistora.

NOR Gate pomocou dvoch tranzistorov

Obrázok 6 zobrazuje ďalšie hradlo na našom zozname, dvojvstupové hradlo NOR, spolu s jeho pravdivostnou tabuľkou. Podobne ako brány AND a NAND na seba reagujú, obvody OR a NOR robia to isté.

Každá zo zobrazených brán je schopná dodať dostatok pohonu na aktiváciu aspoň jedného alebo viacerých susedných tranzistorových brán.

Aplikácie tranzistorového logického hradla

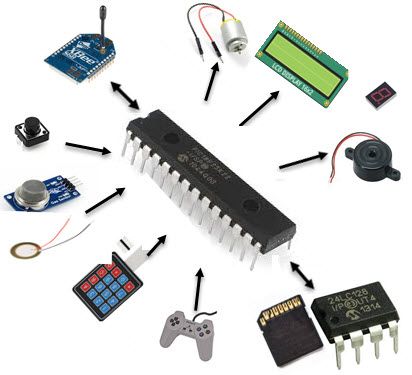

Čo robíte s vyššie vysvetlenými digitálnymi obvodmi, ktoré teraz vlastníte? Čokoľvek, čo by ste mohli dosiahnuť s konvenčnými bránami TTL alebo CMOS, ale bez obáv z obmedzení napájacieho napätia. Tu je niekoľko aplikácií tranzistorových logických brán v akcii.

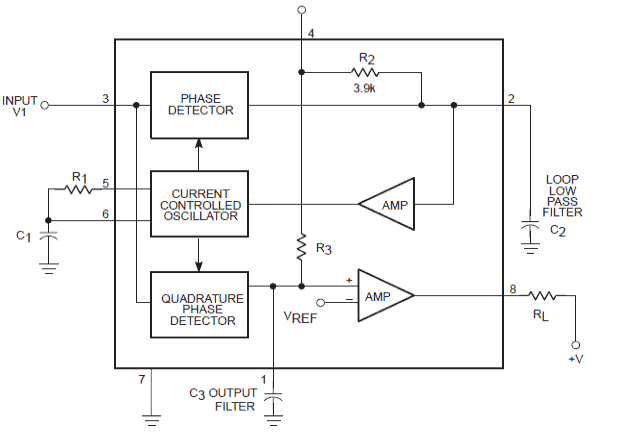

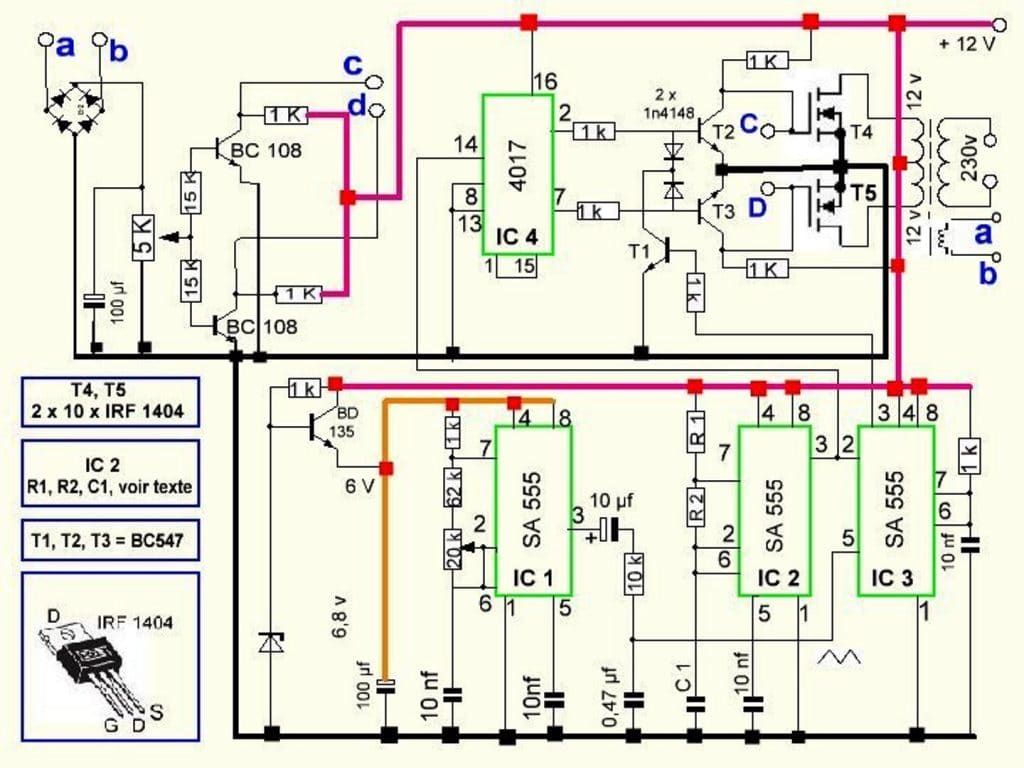

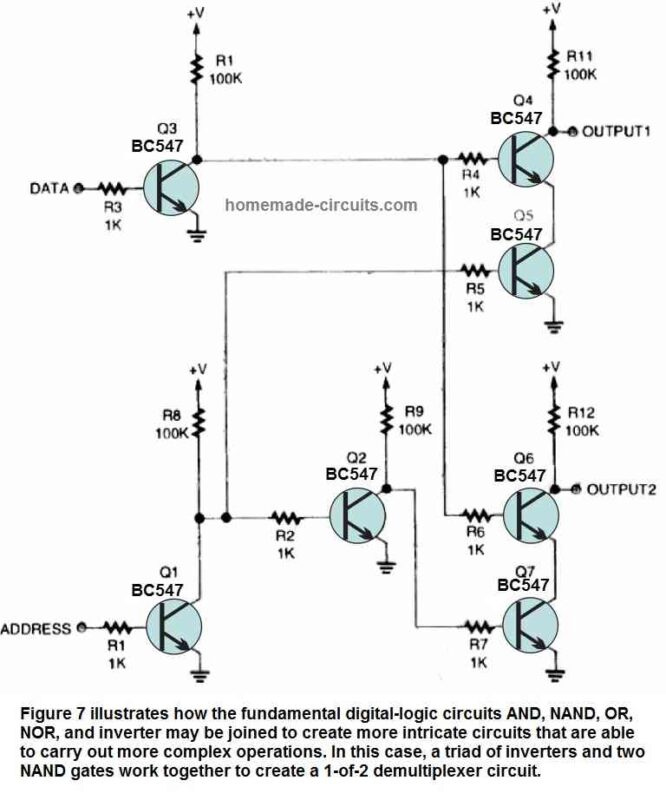

Obvod demultiplexora

1-z-2 demultiplexor s tromi bránami NOT a dvoma obvodmi NAND je znázornený na obrázku 7. Príslušný výstup sa vyberie pomocou jednobitového „adresového vstupu“, ktorým môže byť buď OUTPUT1 alebo OUTPUT2, pričom sa aplikujú riadiace informácie. do obvodu pomocou vstupu DATA.

Obvod funguje najefektívnejšie, keď je rýchlosť prenosu dát nižšia ako 10 kHz. Funkčnosť okruhu je jednoduchá. Vstup DATA je napájaný požadovaným signálom, ktorý zapína Q3 a invertuje prichádzajúce dáta na kolektore Q3.

Výstup Q1 je zosilnený, ak je vstup ADDRESS nízky (uzemnený alebo nie je poskytovaný žiadny signál). Na kolektore Q1 je vysoký výkon rozdelený do dvoch ciest. V prvej ceste je výstup Q1 privedený do základne Q5 (jednej z nôh dvojvstupovej brány NAND), čím sa zapne a tým sa „aktivuje“ brána NAND tvorená Q4 a Q5.

V druhej ceste je vysoký výstup Q1 súčasne privádzaný do vstupu ďalšieho hradla NOT (Q2). Po dvojitej inverzii sa výkon Q2 zníži. Toto nízke napätie je napájané základňou Q7 (jeden terminál druhého hradla NAND, tvoreného z Q6 a Q7), čím sa vypína obvod NAND.

Akákoľvek informácia alebo signál aplikovaný na DATA vstup za týchto okolností prichádza na OUTPUT1. Prípadne je situácia opačná, ak sa na vstup ADDRESS dostane vysoký signál. To znamená, že všetky informácie poskytnuté obvodu sa zobrazia na OUTPUT2, pretože hradlo NAND Q4/Q5 je vypnuté a hradlo NAND Q6/Q7 je povolené.

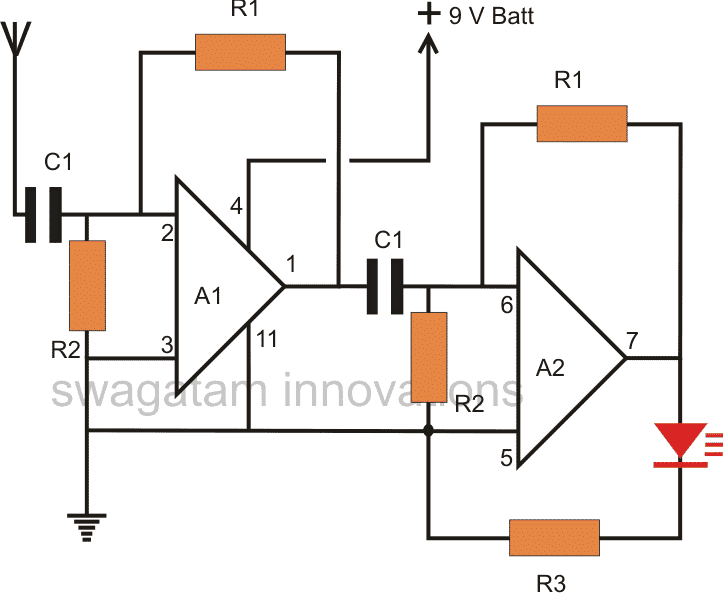

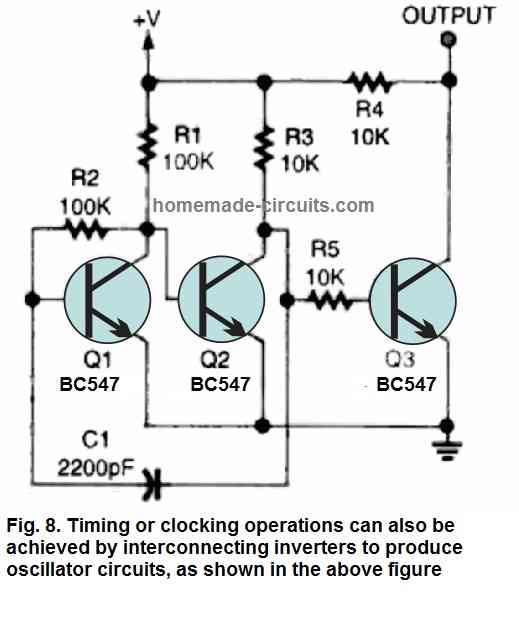

Oscilačný obvod (generátor hodín)

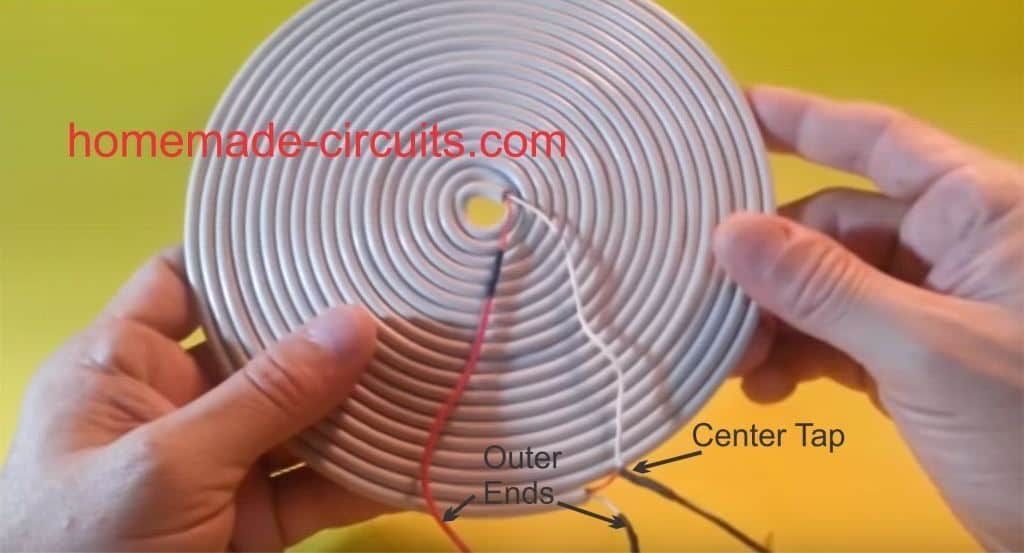

Naša ďalšia aplikácia logického hradla tranzistora, znázornená na obr. 8, je základný generátor hodín (tiež známy ako oscilátor) vyrobený z troch obyčajných hradlových invertorov NOT (jeden z nich je predpätý pomocou spätnoväzbového odporu R2, ktorý ho vloží do analógová oblasť).

Na vyrovnanie výstupu je zahrnuté tretie hradlo NOT (Q3), ktoré dodáva doplnok k výstupu oscilátora. Hodnota C1 sa môže zvýšiť alebo znížiť, aby sa zmenila prevádzková frekvencia obvodu. Výstupný tvar vlny má frekvenciu približne 7 kHz s V+ pri 1,5 voltoch jednosmerného prúdu pri použití uvedených hodnôt komponentov.

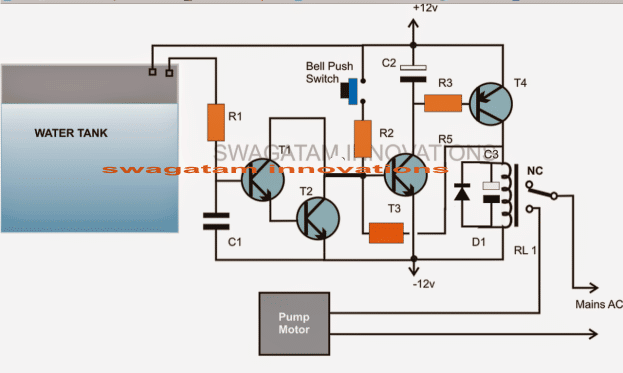

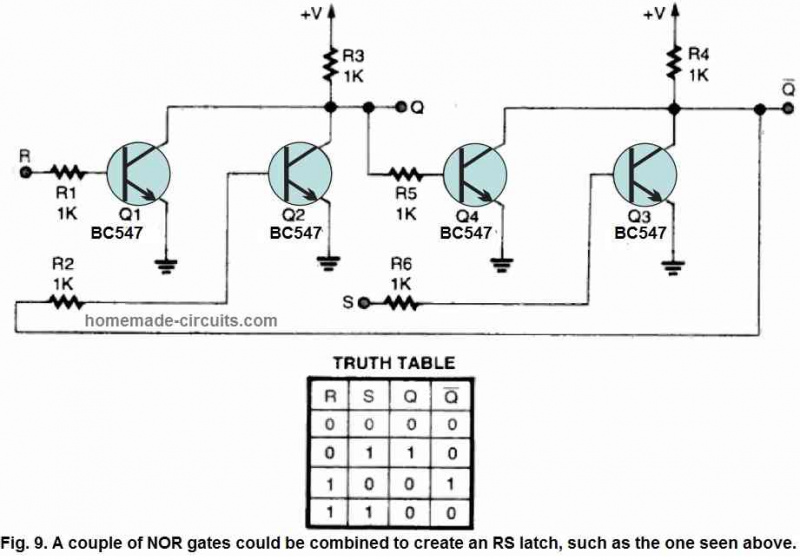

Obvod západky RS

Obr. 9 ukazuje náš konečný aplikačný obvod, západku RS, ktorú tvoria dve hradla NOR. Aby sa zabezpečil zdravý výstup na výstupoch Q a Q, odpory R3 a R4 sú nastavené na 1k ohmov.

Pravdivostná tabuľka západky RS je zobrazená vedľa schematického návrhu. Toto je len niekoľko ilustrácií niekoľkých dôveryhodných, nízkonapäťových, digitálnych obvodov s logickým hradlom, ktoré môžu byť vytvorené pomocou jednotlivých tranzistorov.

Obvody využívajúce tranzistorovú logiku potrebujú príliš veľa častí

Mnoho problémov je možné vyriešiť pomocou všetkých týchto nízkonapäťových tranzistorových logických obvodov. Avšak použitie príliš veľkého množstva týchto tranzistorových brán by mohlo viesť k novým problémom.

Počet tranzistorov a rezistorov môže byť dosť veľký, ak aplikácia, ktorú vytvárate, obsahuje veľké množstvo brán, ktoré zaberajú cenný priestor.

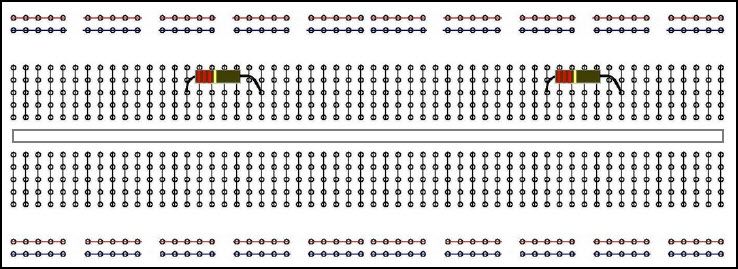

Použitie tranzistorových polí (veľa tranzistorov uzavretých v plaste) a rezistorov SIP (Single Inline Package) namiesto jednotlivých jednotiek je jedným zo spôsobov, ako vyriešiť tento problém.

Vyššie uvedený prístup môže ušetriť tonu miesta na doske plošných spojov pri zachovaní výkonu, ktorý sa rovná výkonu ich ekvivalentov v plnej veľkosti. Tranzistorové polia sú ponúkané v balení na povrchovú montáž, 14-kolíkový priechodný otvor a balenie po štyroch.

Pre väčšinu obvodov môžu byť typy zmiešavacích tranzistorov celkom prijateľné.

Napriek tomu je vhodné, aby experimentátor pracoval s jedným typom tranzistora na zostavenie tranzistorových logických obvodov (to znamená, že ak vytvoríte časť hradla pomocou BC547, skúste použiť rovnaký BJT aj na výrobu ostatných zostávajúcich hradel).

Dôvodom je, že rôzne varianty tranzistorov môžu mať trochu odlišné vlastnosti, a preto sa môžu správať odlišne.

Napríklad pre niektorý tranzistor môže byť limit zapnutia základne väčší alebo menší ako iný, alebo môže mať celkový prúdový zisk o niečo vyšší alebo nižší.

Na druhej strane, náklady na nákup hromadnej skrinky jedného typu tranzistora by mohli byť tiež nižšie. Výkon vašich obvodov sa zvýši, ak sú vaše logické brány postavené pomocou zodpovedajúcich tranzistorov a projekt ako celok bude v konečnom dôsledku prínosnejší.